MOSFETのゲート電荷測定方法

パワーMOSFETは、高速スイッチング・デバイスを含む様々な用途で使用されている。デバイスのスイッチング速度は、内部容量によって影響を受け、通常その容量値は入力ゲートCgsおよびドレイン容量Cgdから導出されるCissおよびCossという項目でデータシートに記載される。それらの容量を特定することに加えて、ゲート電荷(QgsおよびQgd)でもMOSFETのスイッチング性能を評価することができる。

MOSFETのゲート電荷を測定する1つの方法がJEDEC JESD24-2規格 「Gate Charge Test Method」に記載されている。この方法では、ゲート電流を与えた状態で、ゲート・ソース間電圧を時間の関数として測定し、ゲート電圧波形の結果からゲート-ソース電荷(Qgs)、ゲート-ドレイン電荷(Qgd)、およびゲート電荷(Qg)を導出する。

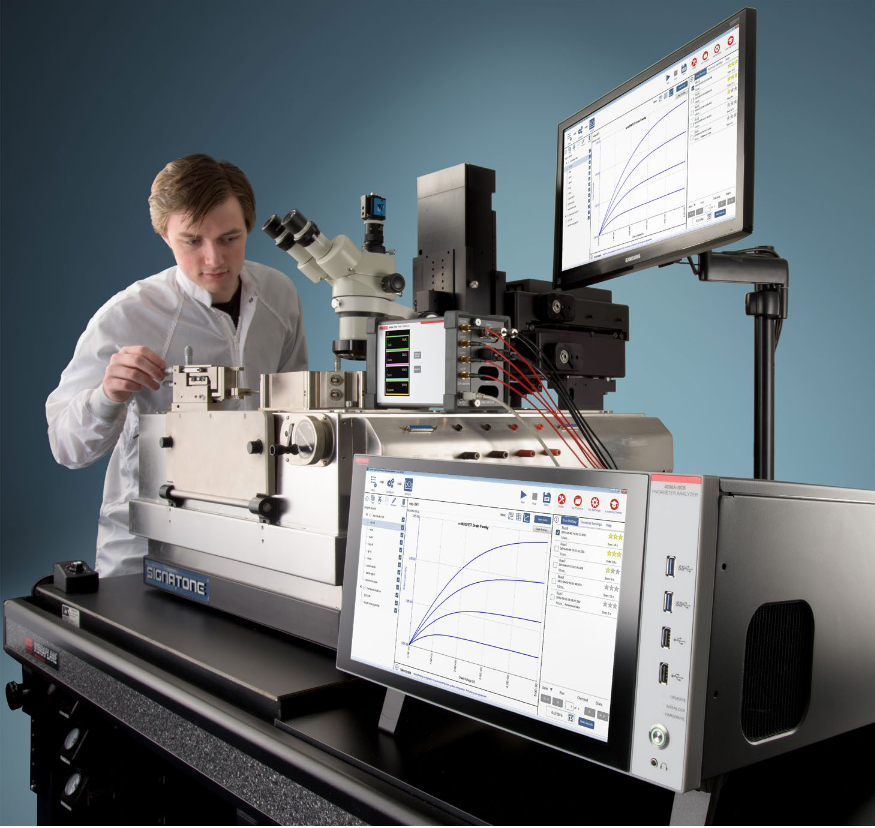

4200A-SCSパラメータ・アナライザの2つのソース・メジャー・ユニット(SMU:source measurement unit)と、システムに含まれるゲート電荷測定用テストライブラリを使用し、MOSFETのゲート電荷測定を行 う こ と が で き る。ま た、 こ の テ ス ト は、4200A-SCS Clarius+ Software Suiteで提供される多くのテストライブラリの1つである。本アプリケーション・ノートでは、4200A-SCSパラメータ・アナライザを用い、JEDECに準拠したゲート電荷測定に基づく、MOSFETのゲート電荷測定方法を解説する。

ゲート電荷測定の概要

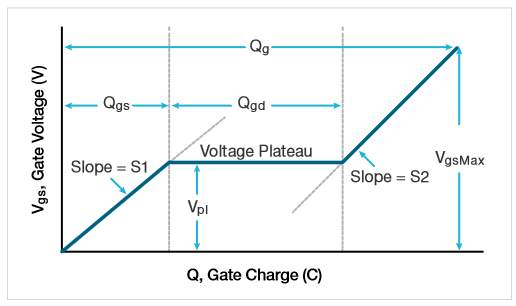

ゲート電荷測定法は、一定のテスト電流(Ig)をMOSトランジスタのゲートに流し、ゲート-ソース電圧測定値(Vgs)とゲートに流入する電荷値に対してプロットする。ドレイン端子には一定の電圧バイアスを印加する。図1に、パワーMOSFETのゲート電圧対ゲート電荷を示す。

ゲート電荷(Q)は、印加したゲート電流および時間(Igdt)から導出される。ゲート-ソース電荷(Qgs)は、図1に示すように、電圧(Vgs)がほぼ一定である平坦領域の始まりに達するまでに必要な電荷である。平坦(またはミラー)電圧(Vpl)は、JEDEC規格に従い、dVgsが最小のときのゲート-ソース間電圧で定義される。トランジスタがオフ状態からオン状態にスイッチングしている時にその電圧が平坦となる。また、このスイッチングを完了するのに必要なゲート電荷、すなわち、デバイスを平坦領域の開始から終了に切り替えるのに必要な電荷は、ゲート-ドレイン電荷(gate-drain charge)(Qgd)として定義され、ミラー電荷として知られている。ゲート電荷(Qg)は、原点からゲートVgsが指定した最大値(Vgs)が指定した最大値(VgsMax)と等しくなるまでの電荷である。

S1は、原点から最初の平坦点までの傾きで、S2は、最後の平坦点から指定した最大ゲート電圧(VgsMax)までの傾きである。それらの傾きは、JESD24-2規格に規定されるように、QgsおよびQgdを計算するために使用される。

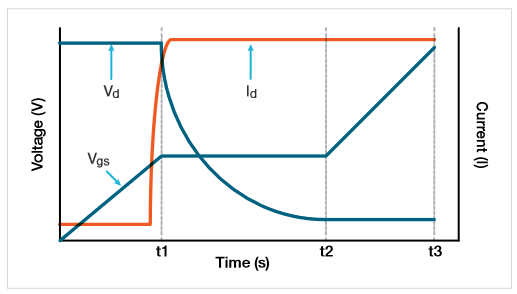

図2に、典型的な時間に対するゲートおよびドレイン波形を示す。電流をゲートに与えると、Vgsは閾値電圧に達するまで増加する。このとき、ドレイン電流(Id)が流れ始める。時刻t1でCgsが充電されると、Idは一定となり、ドレイン電圧(Vd)は低下する。Vgsは、平坦領域の終わりまで一定のままである。Cgdが時間t2で充電されると、ゲート-ソース電圧(Vgs)は、指定された最大ゲート電圧(VgsMax)に達するまで再び増加し始める。

半導体パラメータ・アナライザを使用したゲート電荷測定

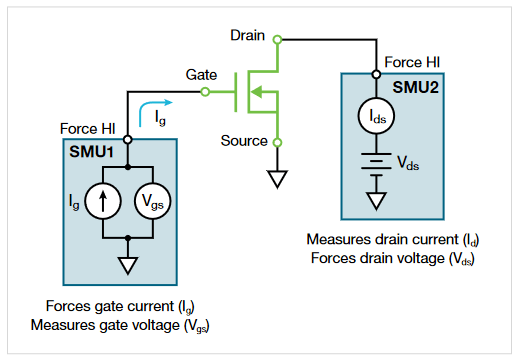

4200A-SCSの2つのSMUを使用してパワーMOSFETのゲート電荷を測定する。図3にゲート電荷測定の基本回路図を示す。SMU1のフォースHI端子をMOSFETのゲート端子に接続し、ゲート電流(Ig)を印加し、ゲート-ソース電圧(Vgs)を時間の関数として測定する。SMU2は、特定の電流コンプライアンス(Ids)を設定し一定の電圧(Vds)をドレインに印加する。4200-SMUの最大コンプライアンス電流は0.1Aで、4210-SMUの最大コンプライアンスは1Aである。

ゲート電荷試験中、ゲート電圧は増加し、トランジスタをオンにする。平坦領域の間、電流が特定のコンプライアンスレベルに達するため、ドレインSMU(SMU2)は、電圧制御から電流制御モードに切り替わる。ソフトウェアは、オフ状態からオン状態への遷移の間、ドレイン電流過渡現象およびドレイン電圧の結果を返す。

MOSFETのソース端子は、4200A-SCS筐体のForce LO端子またはGNDUに接続する

Clarius+ ソフトウェアでのゲート電荷測定の設定

ゲート電荷測定は、テスト・ライブラリとプロジェクト・ライブラリの両方に置かれ、これは、“gate charge” というキーワードで検索することによって選択枠から見つけることができる。テスト・ライブラリでテストが見つかると、それを選択しプロジェクト・ツリーに追加することによって、プロジェクト上で運用できる。このテストは、gate_chargeユーザライブラリのgate_charge ユーザモジュールから作成されている。

入力パラメータ

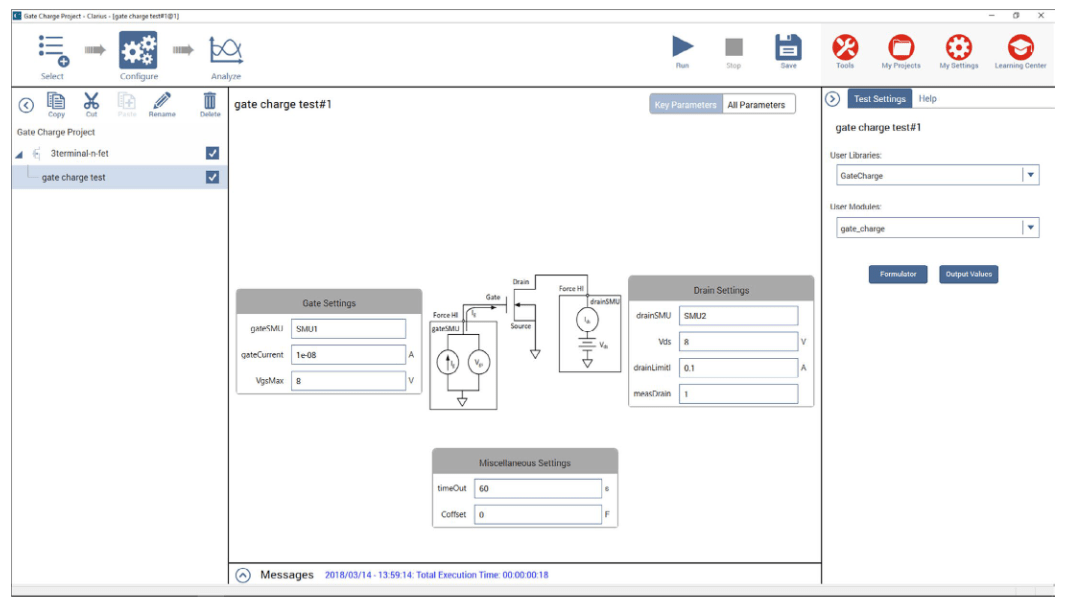

テスト実行前に、クラリウスソフトウェアのConfigure画面(図4)で入力テスト・パラメータを入力する。入力パラメータはデバイスおよび、どのモデルのSMUが使用されるかに依存する。

表1に 入 力 パ ラ メ ー タ の 説 明 を 示 す。 ま ず、MOSFETの ゲ ート(gateSMU)とドレイン(drainSMU)に接続されたSMU番号を入力する。ソース端子を常にGNDUまたはForce LOに接続する。

gateCurrent (Ig) パラメータは、ゲートSMUによってゲートに印加される電流の大きさを示す。ドレイン電圧(Vds)は、ドレインに印加されるバイアス電圧であり、drainLimitIはドレインSMUのコンプライアンス電流である。

Coffsetは、オフセットキャパシタンスを補正するために使用され、次にそれを解説する。

表1. gate_charge ユーザモジュールの入力パラメータ

| 入力パラメータ | 値の範囲 | デフォルト値 | 概要 |

| gateSMU | SMU1-SMU9 | SMU1 | ゲート端子に接続されたSMU番号 |

| drainSMU | SMU1-SMU9 | SMU2 | ドレイン端子に接続されたSMU番号 |

| ソース | GNDU | GNDU | ソース端子は常にGNDUのForce LO端子に接続 |

| Vds | ±200V | 10 V | ドレインSMUのドレインバイアス電圧の大きさ |

| drainLimitI | 4200-SMU: 0.1A 4210-SMU: 1 A |

0.1 A | ドレインSMUの電流コンプライアンス |

| gateCurrent | ± 1E-5 A | 1e-7 A | ゲートSMUのゲート電流の大きさ |

| VgsMax | ±200V | 10 V | ゲートSMUの最大電圧 |

| タイムアウト | 0~300 s | 60 s | タイムアウト時間 |

| measDrain | 1 (yes) or 0 (no) | 1 | ドレイン電流値を返す |

| Coffset | 0 or Ceff | 0 | オープン回路でテストを実行し、シートに返された |

オフセット容量の補正

測定システムのケーブル配線および接続に応じて、一桁pFから数百pFの範囲でオフセット容量が存在する。これらの容量は、オープン回路でgate_charge ユーザモジュールを実行し、オフセット容量を求め、補償用ソフトウェアのオフセット容量値に入力することで補正することができる。これらのステップの実行方法を次に示す。

- オフセット容量を測定する: 入力ゲート電流を含むテストパラメータを、あたかもデバイスがSMUに接続されたかのように設定する。Ceff 測定に対しVgsMaxを増加させる。試験を行う前に、プローブを持ち上げるか、テスト・フィクスチャからデバイスを取り外す。オープン回路でゲート電荷測定を実行する。

- オフセット容量を求める:テストの実行後、オフセット容量値が計算され、シートのCeff 列に表示される。Ceffは、最大ゲート電圧、ゲート電流、および時間から導出される。このステップ中はオープン回路が測定されるため、テストが実行された後、シートに-9または-12のテストステータス値が表示される。これは、デバイスが測定されないことにより平坦領域が存在しないためである。しかし、そのCeff 値は正しく、Configure画面にCoffsetとして入力する。

- 測定されたオフセット容量を入力し、実行する: Configure画面にCoffsetの測定オフセット容量Ceff を入力する。デフォルトでは、Coffsetは0Fである。後に続く読み取り処理でオフセット容量に対して補償が行われる。

テストの実行

入力パラメータを入力し、画面上部のRunを選択してテストを実行する。テストが実行されると、ゲート電荷波形はAnalyze画面のグラフにリアルタイムで更新され、計算された出力パラメータはシートに表示される。

出力パラメータ

テスト完了後、いくつかのパラメータがシートに返される。表2にそれらのパラメータを解説する。

表2. gate_charge ユーザモジュールの出力パラメータ

| 出力パラメータ | 概要 |

| gate_charge | テストステータス値-説明については表3を参照 |

| timeArray | 計測時間(秒) |

| VgArray | ゲート・ソース間電圧測定値(ボルト) |

| VgCharge | ゲート電荷測定値(クーロン) |

| VdArray | ドレイン電圧測定値(ボルト) |

| IdArray | ドレイン電流測定値(アンペア) |

| スロープ | ゲート電圧の動的傾き(dVg/dt) |

| Ceff | 最大ゲート電圧に対するゲート電荷の比率 |

| Vpl | 平坦またはミラー電圧(ボルト) |

| T1 | 平坦領域が開始するタイムスタンプ(秒) |

| T2 | 平坦領域が終了するタイムスタンプ(秒) |

| Qgs | 原点から最初の変曲点、すなわち電圧平坦領域までのゲート電荷(クーロン) |

| Qgd | ゲート電荷曲線の2つの変曲点間のゲート電荷(クーロン) |

| Qg | 原点からVgsMaxまでのゲート電荷(クーロン) |

結果のグラフ化

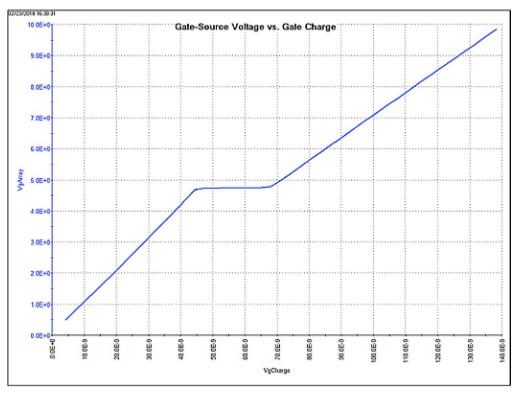

結果として得られるゲート-ソース電圧は、ゲート電荷の関数としてプロットすることができ、また、ドレイン電流およびドレイン電圧は、時間の関数としてプロットすることができる。図5は、4200A-SCSによって生成される典型的なゲート電圧波形である。

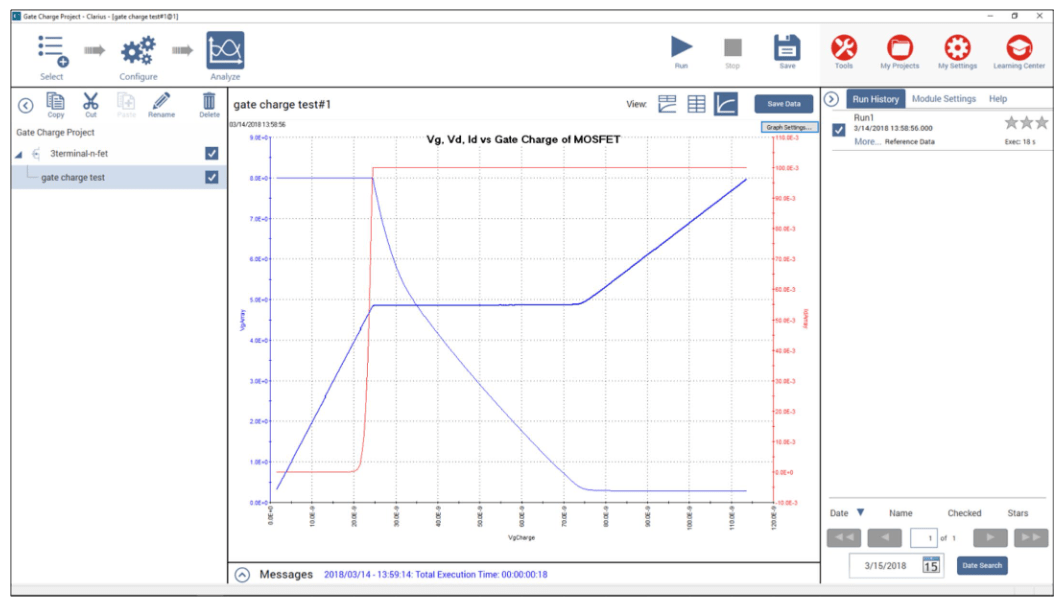

Vgsのプロットに加えて、VdsおよびIdも、ゲート電荷または時間の関数としてプロットすることができる。図6に、ゲート電荷の関数として3つのパラメータの全てがプロットされたクラリウスソフトウェアのAnalyze画面におけるグラフを示す。この場合、電圧はY1軸上に示され、電流はY2軸上にプロットされる。

テストステータスの確認

テストが実行されるたびに、テストステータス値が “gate_charge” と名付けられたシートの第1列に返される。表3に“gate_charge” 列に返されたテストステータス値と、それらの説明および注釈を示す。

表3. テストステータス値

| テスト状況 | 概要 | 注 |

| 1 | エラーなし。 | テストは成功。 |

| -1 | ゲートSMUなし。 | 正しいSMUを指定する。 |

| -2 | ドレインSMUなし。 | 正しいSMUを指定する。 |

| -3 | VgsMax > 200 V | ゲート電圧が200V 未満であることを確認する。ゲート電圧を下げる。 |

| -4 | ドレイン電流制限が1A(4210-SMU)を超える。 ドレイン電流制限が0.1A(4200-SMU)を超える。 |

ドレイン電流が1A(中電力SMUでは0.1A)未満であることを確認する。ドレイン電流制限を下げる(drainLimitI)。 |

| -5 | 電力の制限を超える。 | V>20Vの場合、電流上限を<0.1Aとする。ドレイン電流制限(drainLimitI)またはドレイン電圧(Vds)を減らす。 |

| -6 | 入力条件のエラーチェック。タイムアウトを200秒に制限する。 | タイムアウトを<200秒に指定する。 |

| -7 | 試験時間が規定のタイムアウト(timeOut)を超える。 | タイムアウトを増やす。最大値は200秒。gateCurrentを増やしてデバイスをより高速に充電するように試みる。 |

| -8 | 反復回数 > 10000 | ゲート電流(gateCurrent)を増加させる。 |

| -9 | 反復回数 < 5 | ゲート電流(gateCurrent)を小さくする。デバイス、テストセットアップ、および正しいSMUを確認する。 このエラーが、オフセット補正のオープン回路測定時に発生した場合無視することができる。Ceff 値は有効。 |

| -10 | 原点から最初の平坦点までの点数が< 10 | ゲート電流(gateCurrent)を減らす。 |

| -11 | 傾きS1の計算エラー。相関係数< 0.9。原点から最初の平坦点までの曲線が直線ではない。 | デバイスとテストの設定を確認。 |

| -12 | 傾きS2の計算エラー。相関係数< 0.9。最後の平坦点からVgsMaxまでの曲線が直線ではない。 | デバイスとテストの設定を確認。VgChargeまたはVdArrayが高い場合は、gateCurrentを減らしてテストを繰り返す。 このエラーが、オフセット補正のオープン回路測定時に発生した場合無視することができる。Ceff 値は有効。 |

| -13 | Vds > 200 V | ドレイン電圧を下げる。 |

| -14 | gateCurrent > 10 µA | ゲート電流(Ig)を減らす。 |

結論

トランジスタのゲート電荷測定は、4200A-SCSパラメータ・アナライザを用いて容易に行うことができる。デバイスのゲートおよびドレインにそれぞれSMUを接続し、クラリウスソフトウェアを使用し、ゲート電荷波形を容易に導出する。