與我們聯絡

與 Tek 業務代表即時對談。 上班時間:上午 6:00 - 下午 4:30 (太平洋時間)

請致電

與 Tek 業務代表即時對談。 上班時間:上午 8:30 - 下午 5:30 (太平洋時間)

下載

下載手冊、產品規格表、軟體等等:

意見回饋

精確、可重複的 PCIe 量測

近二十年來,PCI Express® 科技一直是被廣泛採用的高速串列介面連接標準。最新 PCIe® 規格可滿足資料密集型的市場需求,例如人工智慧/機器學習及高效能運算。

我們的 PCIe 自動化測試解決方案,可藉由解決設定及校驗問題來大幅降低測試複雜性。這些解決方案結合低雜訊量測硬體,可達成快速、準確且可重複的量測。身為 PCI-SIG® 工作群組的現任投票成員,我們擁有發射器、接收器、參考時脈和鎖相迴路 (PLL) 驗證所需的專業知識。

PCI Express、PCIE 和 PCI-SIG 是 PCI-SIG 的註冊商標和/或服務標誌。

PCIe 全方位自動化測試解決方案

領先業界的 PCIe 6.0 Base 和 CEM 發射器與接收器測試解決方案

PCIe® 6.0 是一種多功能、高速串列介面標準,用於串連現代運算系統中的各種元件。它利用 PAM4 訊號和前向錯誤更正 (FEC) 實現突破性的 64.0 GT/s 資料傳輸速率,為要求嚴苛的各類應用提供更快的處理速度和更流暢的效能。

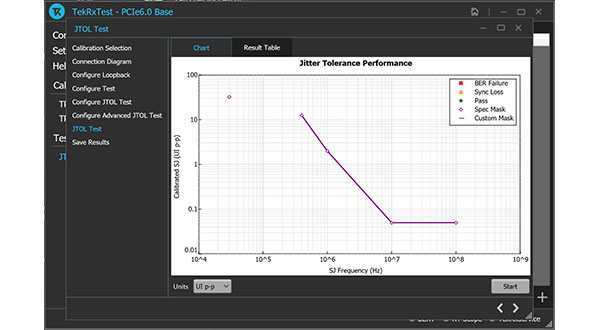

Tektronix 的直覺式工具提供開箱即用的量測支援,包括訊號雜訊失真比 (SNDR)和不相關的抖動,以及最新規範下要求的接收器應力眼圖 TP3/TP2 校正和儀器雜訊補償。

與前幾代產品相同,PCIe 6.0 驗證與相容性測試,對於確保遵守 PCI-SIG 為 BASE 和 CEM 制定的標準至關重要。 Tektronix 的 PCIe 6.0 發射器 (Tx) 測試解決方案 ,可協助工程師解決最新的設計與驗證問題。 對於 PCIe 6.0 接收器 (Rx) 測試解決方案,Tektronix 和 Anritsu 合作,透過將 Tektronix 的 DPO70000SX 即時示波器與 Anritsu 的 MP1900A 誤碼率測試儀 (BERT) 搭配使用,提供卓越的 Rx 測試解決方案,兩者都由 Tektronix 開發及支援的測試自動化和分析工具控制。

PCIe 發射器測試解決方案

我們的 PCIe 發射器測試解決方案,透過提供從 2.5 GT/s 到 64.0 GT/s (Gen 1 到 Gen 6) 的 PCIe 發射器驗證及合規性解決方案,來維持向後相容性。支援從早期矽電壓/時序特性到平台位準發射器及參考時脈量測的頻距。Tektronix 技術領導者透過整合所有工程變更通知 (ECN) 並支援 PCI-SIG 合規研討會作為經批准的解決方案,確保這些解決方案保持相關性。

PCIe 接收器與 PLL 測試解決方案

由於在高損耗通道上校驗壓力眼圖訊號需要極高的靈敏度,PCIe 接收器的驗證極為困難。Tektronix 的 PCIe 接收器測試解決方案讓您確信您的設計已在所需的誤碼率 (BER) 目標下進行了全面測試。我們的直覺式分步工具為 Anritsu MP1900A BERT 提供連結訓練程序,確保您的接收器獲得準確的測試。自動化測試支援壓力眼圖校驗、最新的發射器與接收器連結等化合規性測試( equalization compliance tests)、自訂 BER 執行,以及抖動容差特性分析。此架構也支援簡易發射器 PLL 頻寬與峰值量測。

Compute Express Link (CXL)

資料中心架構必須更常回應資料移動和存取需求,同時將耗電量降至最低、提高效率,支援更大型及更多元的應用。奠基於 PCIe 強大的實體層,CXL 能滿足這些需求,讓處理器能夠以高效能的方式存取同樣的記憶體資源、彼此溝通,並在單一架構上執行。Tektronix 實體層解決方案支援最快速的 CXL 資料速率 (32 Gt/s) 以及各種外形尺寸,以符合這項新興技術的需求。