與我們聯絡

與 Tek 業務代表即時對談。 上班時間:上午 6:00 - 下午 4:30 (太平洋時間)

請致電

與 Tek 業務代表即時對談。 上班時間:上午 8:30 - 下午 5:30 (太平洋時間)

下載

下載手冊、產品規格表、軟體等等:

意見回饋

分析配電網路 (PDN) 的電源完整性

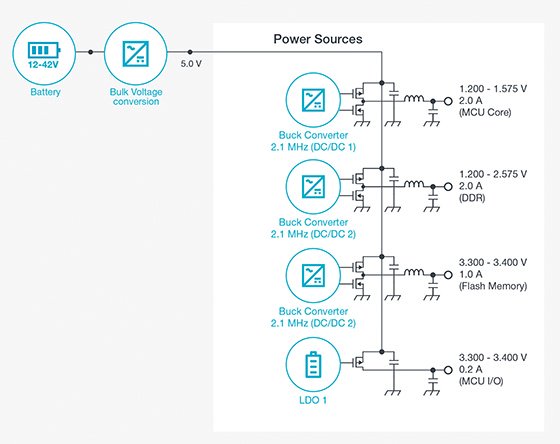

配電網路 (PDN) 必須為靈敏負載 (例如微處理器、DSP、FPGA 和 ASIC) 提供許多低雜訊 DC 電軌。追求更高速度和更高密度意味著更快的邊緣速率、更高的頻率和更多的電軌,以及更低的電壓位準和更高的電流。這會對訊號完整性和電源完整性帶來設計上的壓力。

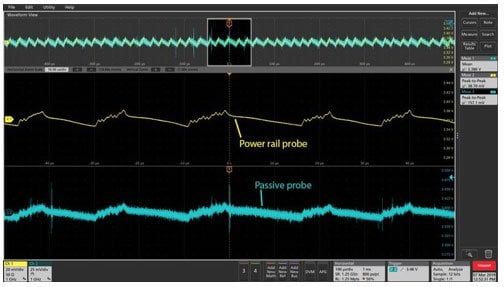

進行電源完整性量測的目的是要驗證在所有預期的運作條件下,達到負載點 (POL) 的電壓和電流是否滿足負載的電軌規格。在 GHz 頻率下準確量測電軌雜訊的毫伏特時,需要特別注意。

在不阻隔直流電或對電軌造成負載的情形下測量高頻漣波

電軌的雜訊規格可能會以毫伏特 (mV) 的振幅上升到 MHz 或 GHz 頻率 範圍。

具有低雜訊貢獻和高頻寬的示波器可以進行這些量測,但是將訊號輸入到 儀器中則具有挑戰性。

示波器隨附的高阻抗 10X 被動式探棒應具有足夠的頻寬,但是會使您嘗試量測的雜訊衰減。然後,示波器會同時放大訊號和量測系統雜訊, 使其無法區分。

1X 探棒會傳遞雜訊 (而不衰減),但會受限於數個 MHz 頻寬。

使用 50 Ω 示波器輸入的傳輸線探棒或纜線可提供出色的高頻率效能, 但 DC 的負載會很大。

用於進行電軌量測的理想探棒,可提供直流高阻抗,並可作為高頻率交流電的 50Ω 傳輸線。 TPR1000 和 TPR4000 等電軌探棒的設計訴求在於以高頻寬因應 這些挑戰,不會造成衰減且沒有最低負載。

處理 1 V 至 48 V 及以上的電源

儘管許多 FPGA 和 SoC 的主電源電壓已急遽下降,但這些並不是唯一要考慮的 電源。晶片 I/O 電源可涵蓋比主邏輯電源更廣的範圍。為 POL 穩壓器或 電壓調節器模組 (VRM) 饋電的批量電源的電壓通常會高許多。

儘管許多示波器和探棒可提供一些直流偏移,但可能不足以處理您系統中的所有 電軌。在較低的每格伏特數 (較高的靈敏度) 設定下,儀器系統傾向支援 較少的偏移。雖然阻隔直流電是一個選項,但通常不是理想的做法 (請參閱上文)。

除了滿足上面概述的高頻需求外,TPR1000 和 TPR4000 等電軌探棒還提供了高偏移範圍 來因應各種電壓位準。

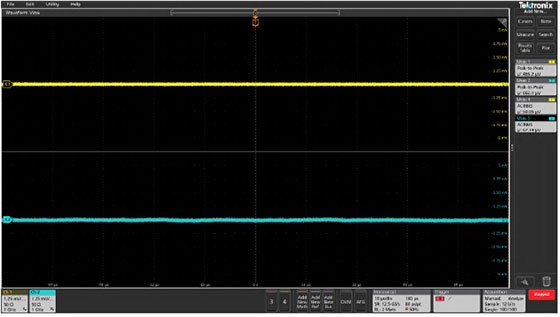

儘量減少量測系統雜訊貢獻

測量 10 mV 次級的雜訊時,需要特別注意量測系統雜訊。如上所述, 使用非衰減或 1X 探棒,可減輕示波器的放大器負擔。示波器的 內部雜訊和量測解析度也扮演很重要的角色。

6 系列 MSO 包括具有領先業界雜訊效能的新前端。示波器提供了 低至 50μV RMS和 466μV 峰值的開放通道雜訊。若與 TPR1000/4000 電軌探針配對, 系統雜訊可低至 70μV RMS。

6 系列會以每秒 12.5 GS 的速率提供 12 位元解析度。高解析度功能會以每秒 625MS 及以下的速率 將解析度提高至 16 位元。4 和 5 系列 MSO 也會提供 12 位元解析度,而使用高解析度模式最高可達 16 位元。

測量配電網路阻抗

對於為 FPGA、處理器和其他復雜 IC 供電的 PDN,電軌阻抗必須很低, 以便提供高電流來回應快速變化的需求。但是,此網路是由許多阻抗所組成, 包括穩壓器、去耦電容器和 PCB 軌跡。高速切換牽涉到寬頻頻率, 而非預期的阻抗變化會導致過多的暫態或雜訊。在較寬的 頻率範圍內測量網路設計的阻抗,可確保網路不會 產生不想要的意外狀況。

傳統上,網路阻抗量測是使用 VNA 來執行,例如可測量 100 kHz 到 6 GHz 的 雙埠 TTR500。

5 和 6 系列 MSO 示波器可使用分析軟體、訊號產生器 (內建或 AFG31000 系列) 和隔離變壓器, 測量低至 10 Hz 的電軌阻抗。

使用同時頻譜和波形分析進行雜訊特性分析

假設您已量測電軌雜訊,而其不符合規格。其來自 直流-直流轉換器? 批量電源?PLL?時脈?串音?頻譜分析可提供 雜訊來源的線索 - 有助於讓雜訊頻率與切換頻率及諧波相關聯。

頻譜分析儀 (例如透過直流阻隔器連接到電軌的 RSA306) 有助於讓您深入了解

雜訊。

示波器上的 FFT 函數也很有用,但這些函數會使用示波器上的取樣時脈,因而難以或不可能同時查看頻譜和電壓波形。

4、5 和 6 系列 MSO 上

獨特的頻譜檢視提供了獨立的頻譜分析儀控制,因此您可同時查看同步的時域頻譜

和頻域波形。

Power rail noise impacts clock and data signal jitter

Noise on power rails often translates into jitter on high-speed data lines. Jitter and power integrity should be analyzed in both the time and frequency domains. Comparing periodic jitter (PJ) frequencies in the TIE spectrum to spurs in the power ripple spectrum is a fast and accurate way to identify signal integrity problems caused by a power distribution network (PDN). This type of analysis requires an oscilloscope with good spectrum analysis capability as well as good jitter analysis.

Learn about using mixed signal oscilloscopes to diagnose jitter caused by power integrity problems

/fig-07-powerrailripple.png?h=548&iar=0&w=975)

使用自動分析軟體進行更快速的電軌量測

即使是進行簡單的量測 (例如數十個電軌上的漣波、過衝和激發), 都需要投注大量時間和關注細節。

5 和 6 系列 MSO 會隨著數位電源管理軟體一起提供,可自動進行這些重複性量測 並產生深入的報告。此軟體還包括抖動分析 (TIE、RJ、DJ 和 Eye 量測), 以檢查由您的 PDN 供電的時鐘和通訊訊號是否過度抖動。

Power Integrity Analysis

Reference System

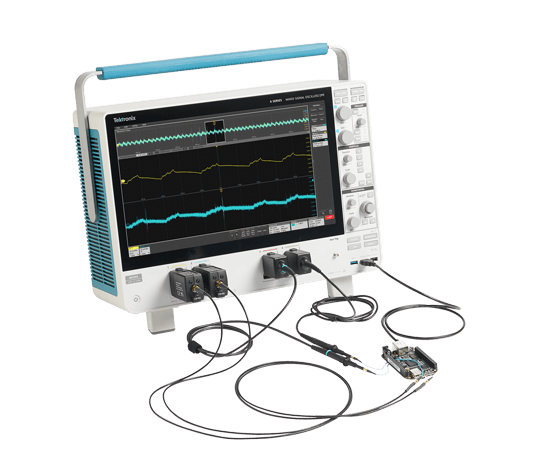

6 Series B MSO

Recommended for exceptionally low noise, 12-bit resolution, and up to 8 channels. From 1 to 10 GHz. Built-in arbitrary/function generator (AFG) recommended for impedance measurements

Noise Analysis

-

DPM software

Optional analysis software automates ripple, overshoot, under-shoot, turn-on, turn-off, time-trend, settling time, and jitter measurements -

TPR Power Rail Probes

Low noise and high offset range at up to 4 GHz with DC offset ranging from -60 to +60 Vdc

Impedance Analysis

-

PWR software

Optional analysis software automates power quality, harmonics, amplitude, timing, switching loss, magnetic analysis, and frequency response analysis (control loop analysis, PSRR and impedance) measurements -

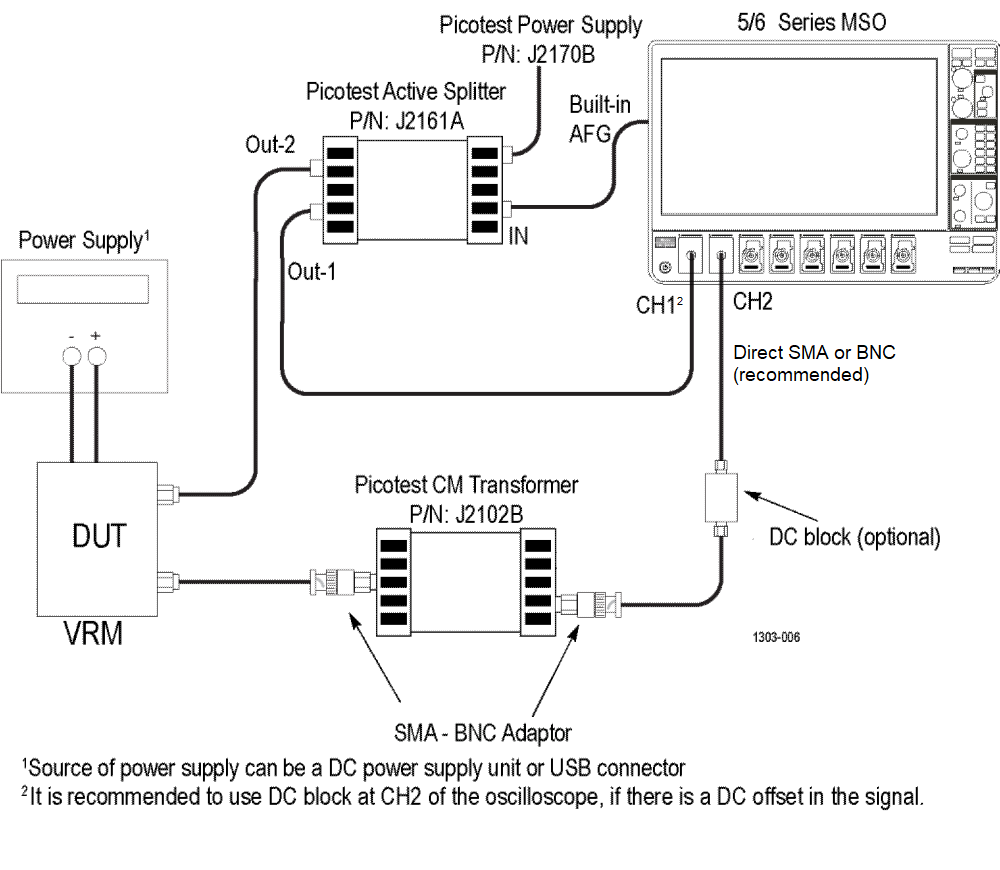

Active Splitter (e.g Picotest J2161A, not shown)

Splits signal from oscilloscope’s AFG into an oscilloscope input channels and into the power rail under test. -

Common Mode Transformer (e.g. Picotest J2102B-BNC, not shown)

Eliminates ground loop error in 2-port shunt-through impedance measurements.