お問い合わせ

ダウンロード

マニュアル、データシート、ソフトウェアなどのダウンロード:

フィードバック

正確で再現性のあるPCIe測定

PCI Express®技術は20年近くにわたり、高速シリアル・インタフェース接続で広く採用されている規格です。最新のPCIe®仕様は、人工知能/機械学習や高性能コンピューティングなどのデータ集約型市場に対応しています。

当社のPCIe自動テスト・ソリューションは、セットアップと機器校正を処理することで、テストの複雑さを劇的に軽減します。低ノイズ測定ハードウェアと組み合わせることで、これらのソリューションは、高速、高精度、再現性のあるシグナル・インテグリティ測定を可能にします。 PCI-SIG®ワーキング・グループのアクティブな投票メンバである当社は、トランスミッタ、レシーバ、リファレンス・クロック、位相ロック・ループ(PLL)検証に必要な専門知識を有しています。

PCI Express、PCIE、PCI-SIGは、PCI-SIGの登録商標および/または商標です。

PCIe向けの包括的な自動テスト・ソリューション

業界をリードするPCIe 6.0ベースおよびCEMトランスミッタおよびレシーバ・テスト・ソリューション

PCIe® 6.0は、最新のコンピュータ・システム内の様々なコンポーネントを接続するために使用される、汎用性の高い高速シリアル・インタフェース規格です。PAM4信号と前方誤り訂正(FEC)を利用して64.0GT/秒という画期的なデータ転送レートを実現し、要求の厳しいアプリケーションの高速処理とスムーズなパフォーマンスを可能にします。

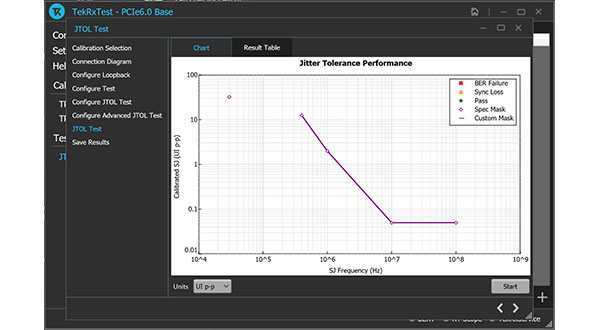

テクトロニクスの直感的なツールにより、信号対雑音歪み比(SNDR)や非相関ジッタの測定、レシーバのストレス・アイ・ビューTP3/TP2の校正、最新の仕様で義務付けられている機器のノイズ比較などを追加設定なしで実行できます。

前世代と同様に、PCIe 6.0の検証およびコンプライアンス・テストは、PCI-SIGによるBASEとCEMの両方の規格への準拠を保証するために不可欠です。テクトロニクスの PCIe 6.0トランスミッタ(Tx)テスト・ソリューションにより、エンジニアは最新の設計/検証の問題に対応できます。PCIe 6.0レシーバ(Rx)テスト・ソリューションでは、テクトロニクスとアンリツの共同作業により、テクトロニクスのDPO70000SXリアルタイム・オシロスコープとアンリツのMP1900Aビットエラーレートテスタ(BERT)を組み合わせて、優れたRxテスト・ソリューションを提供しています。これらは両方とも、テクトロニクスが開発およびサポートするテスト自動化および分析ツールによって制御されます。

PCIe 6.0テスト・アプリケーションについては、お問い合わせください。

PCIeトランスミッタ・テスト・ソリューション

当社のPCIeトランスミッタ・テスト・ソリューションは、2.5GT/s~64.0GT/s(Gen1~Gen6)のPCIeトランスミッタ検証およびコンプライアンス・ソリューションを提供することにより、下位互換性を維持します。初期のシリコン電圧/タイミング特性評価からプラットフォーム・レベル・トランスミッタ、リファレンス・クロック測定まで、サポートは多岐にわたります。テクノロジ・リーダであるテクトロニクスは、すべての設計変更通知(ECN)を組み込み、PCI-SIGコンプライアンス・ワークショップを承認済みソリューションとしてサポートすることにより、ソリューションの関連性を維持します。

PCIe Gen 5トランスミッタ・コンプライアンス・テストのブローシャを見る

DPO70000SXシリーズATIパフォーマンス・オシロスコープ

PCIeレシーバおよびPLLテスト・ソリューション

PCIeレシーバの検証は、高損失チャンネル全体でストレス・アイ信号を校正する感度により、きわめて困難なことで有名です。テクトロニクスのPCIeレシーバ・テスト・ソリューションにより、設計が要求ビット・エラー・レート(BER)ターゲットで十分にテストされているという信頼性がもたらされます。当社の直感的なステップバイステップ・ツールは、アンリツMP1900A BERTのリンク・トレーニング・ルーチンを実行し、レシーバが正確にテストされていることを保証します。自動テストは、ストレス・アイ校正、最新のトランスミッタおよびレシーバ・リンク・イコライゼーション・コンプライアンス・テスト、カスタムBERの実行、ジッタ許容特性評価をサポートします。このフレームワークは、トランスミッタのPLL帯域幅とピーキング測定にも容易に対応します。

DPO70000SXシリーズATIパフォーマンス・オシロスコープ

コンピュート・エクスプレス・リンク(CXL)

データセンタ・アーキテクチャは、電力を最小限に抑え、効率性を高め、より大規模で多様なアプリケーションをサポートしながら、ますます増加するデータ移動とアクセス要求に対応する必要があります。CXLは、PCIe物理層の強度に基づいて構築されており、プロセッサが同じメモリ・リソースに効率的にアクセスし、互いに通信して、単一のアーキテクチャで動作するという要件に対応しています。テクトロニクスの物理層ソリューションは、この新たに生まれた技術に期待される最速のCXLデータ・レート(32 GT/s)と多様なフォーム・ファクタをサポートします。

DPO70000SXシリーズATIパフォーマンス・オシロスコープ