スマート・フォンからサーバまで、ほとんどすべての電子デバイ スには、なんらかの形式のRAMメモリが使用されています。フラッ シュ型NANDはさまざまな民生家電で今も数多く使われています が、コンピュータやコンピュータベースの製品においては今なお SDRAMはメモリ技術の主流となっており、ビット単価も比較的 安価でスピードとストレージ容量のバランスも優れています。ス ピードの高速化、大容量化を実現しつつ、低コスト、低予算、メ モリ・デバイスの寸法の小型化を求める企業にとって、DDR (Double-Data-Rate) SDRAMは今日の主流となるメモリ技術で あり、今なお進化しています。

クロック・レート、データ転送速度が高速になるにつれ、システ ム性能や、システム内のメモリやメモリ制御デバイスのインター オペラビリティ(相互接続性)を確保しなければならない設計エン ジニアにとっては、メモリ・サブシステムのアナログ・シグナル・ インテグリティ(信号忠実度)がますます重要になっています。 プロトコル・レイヤで発見される多くの性能問題であっても、シ グナル・インテグリティ問題として追跡することができます。し たがって、メモリ・デバイスのアナログ検証は、電気回路設計の 検証においてますます重要なプロセスになっています。

メモリ・デバイスの検証で必要となるジッタ、タイミング、電気 的な信号品質テストの詳細は、JEDEC(Joint Electron Device Engineering Committee)で規定されています。それぞれのメ モリ技術のJEDEC仕様で規定されているテストには、クロック・ ジッタ、セットアップ/ホールド時間、信号のオーバーシュート、 アンダーシュート、トランジション電圧などのパラメータなどの 測定が含まれています。しかし、この仕様に対する適合性テスト は複雑であり、時間のかかる作業です。適切なツールや技術があ ればこの作業時間を大幅に短縮することができ、正確な結果を得 ることができます。このアプリケーション・ノートでは、メモリ・ テストの問題を解決し、検証プロセスを簡略化するためのテクト ロニクスのソリューション・ツールキットについて説明します。

| 規格 | JEDEC仕様(最新版) |

| DDR | JESD79F (February 2008) |

| DDR2 | JESD79-2F (November 2009) |

| DDR3 | JESD79-3E (July 2010) |

| LPDDR | JESD209B (February 2010) |

| LPDDR2 | JESD209-2B (February 2010) |

| GDDR5 | JESD212 (December 2009) |

表1. DDR技術におけるJEDEC仕様

信号へのアクセスとプロービング

メモリ検証でまず解決しなければならない問題は、必要な信号へ の接続と信号取込みです。JEDEC規格では、メモリ・コンポーネン トのBGA(Ball Grid Array)半田ボールで測定するように規定さ れています。FBGA(Fine Ball Grid Array)コンポーネントには 半田ボールがありますが、実用的な実装目的のものであり、アク セスできません。どのように対処したらよいのでしょうか。

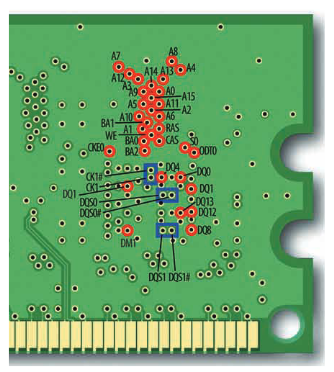

一つの解決方法としては、テストを考慮してPCBレイアウトを設計することであり、基板の裏にメモリ・コンポーネントをプロービングするためのビアを設けます。このテスト・ポイントは厳密にはコンポーネントのボールではありませんが、回路ボードまでのトレース長は十分に短いため、信号劣化は少ないといえます。この方法が可能であればシグナル・インテグリティは良好であり、電気検証も十分なテスト・マージンを持って実行できます。

このようなアプリケーションではハンドヘルド・タイプのプローブを使用することもできますが、電気的に確実に接続したり、同時に複数のテスト・ポイントに接続したりすることは困難です。JEDECの測定では3点以上のテスト・ポイントで測定する必要があり、メモリ・ステートを確認するためにチップ・セレクト、RAS、CASなどの信号も測定することを考えると、半田付けによるプロービングは多くのメリットがあります。

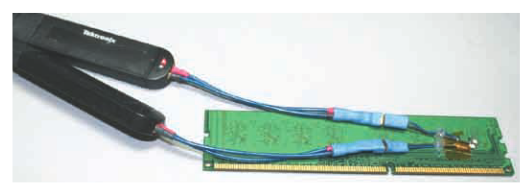

テクトロニクスは、このようなアプリケーションに特化したプロー ビング・ソリューションを開発しました。P7500シリーズには 4GHzから20GHz周波数帯域のプローブまであり、メモリ・アプ リケーションに応じてさまざまな機種が用意されています。図2は、 メモリ・アプリケーションに最適な、P7500シリーズ・プローブ 用のプローブ・チップの例を示しています。マイクロ同軸チップは、 複数のプローブ・チップを半田付けする必要がある場合において も、コスト効果の高いソリューションであり、4GHzまでの優れた 信号忠実度と周波数帯域を実現し、DDR3@1600MT/sまでのメ モリ・デバイスのテストに対応できます。

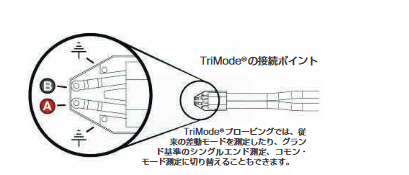

メモリ・アプリケーションでP7500シリーズを使用するもう一つ の利点は、当社特許のTriMode機能にあります。TriModeでは、+ と-間で差動測定が、あるいは信号とグランド間でシングルエン ド測定が行えます。プローブ・チップには3箇所の半田付けポイン トがあり、プローブの切り替えボタンまたはオシロスコープのメ ニュー・コマンドで差動とシングルエンドのモードを切り替える ことができます。メモリ・アプリケーションで有効な利用法の例 として、プローブの+(プラス)をシングルエンド・データまた はアドレス・ラインに接続し、プローブの-(マイナス)をとな りのラインに接続します。こうすることで、2つのシングルエンド 測定モードを切り替えることにより、1本のプローブで2つの信号を測定することができます。

しかし、裏側のビアからは信号にアクセスできない状況が数多くあります。組込みメモリを使った設計では、メモリ部品の反対側に十分なスペースをとることができません。一般的なDIMMであっても、ストレージ密度を上げるために、基板の両面にメモリ部品を搭載しているものも数多くあります。このような状況では、どのようにして信号にアクセスすればよいのでしょうか。

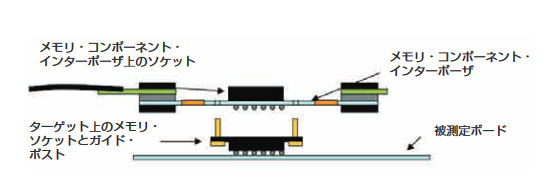

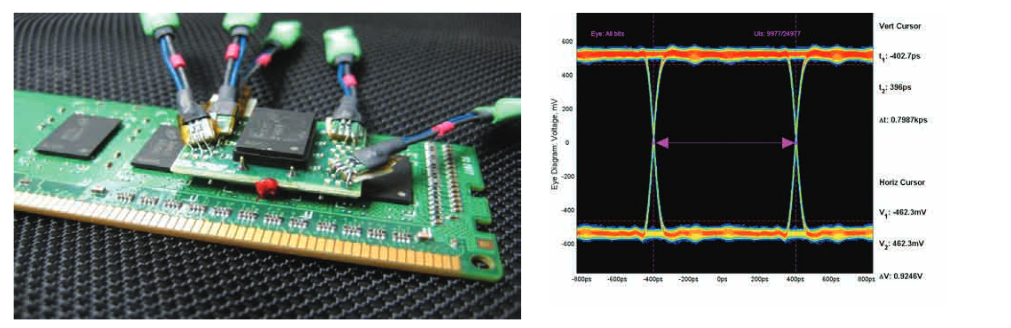

このような状況に対しても新しいプロービング・ソリューション があります。テクトロニクスとNexus Technologies社は、すべ てのDDR3およびDDR2の標準メモリ・デバイスのためのコンポー ネント・インターポーザを開発しました。このインターポーザは ソケット・アーキテクチャを採用しており、メモリICをターゲッ ト基板に半田付けする代わりにこのソケットを半田付けします。 プロービングのためのテスト・ポイントを持ったインターポーザ をこのソケットにはめ込みます。メモリICはインターポーザの上 に実装されているソケットに装着します。図4に、接続の様子を示 します。

Nexus社のインターポーザのユニークな特長の1つは、特許取得のソケットを使用している点です。装着時はメモリICの半田ボールに勘合し、外した時はそれぞれの半田ボールが元の部品に残るようになっています。これにより、半田を取り去ったり、再半田することなく、メモリICを外したり取り付けたりすることができます。使いやすさが向上し、何回も半田を付け外しすることによる電気的な接触不良の可能性を大幅に低減することができます。

インターポーザ内のメモリ部品のBGAパッドのすぐそばには、小さな絶縁抵抗が組込まれています。この抵抗はP7500シリーズのプローブ・チップの電気的なネットワークとマッチングがとれているため、優れた信号忠実度を実現しています。図5のアイ・ダイアグラムは、写真に示すものと同様のDDR3-1333 DIMMに取り付けたインターポーザによって取込んだものです。オシロスコープのデジタル・フィルタ機能により、このプロービング・システムによるわずかなアナログ的影響も除去することができます。

デジタル・プロービング

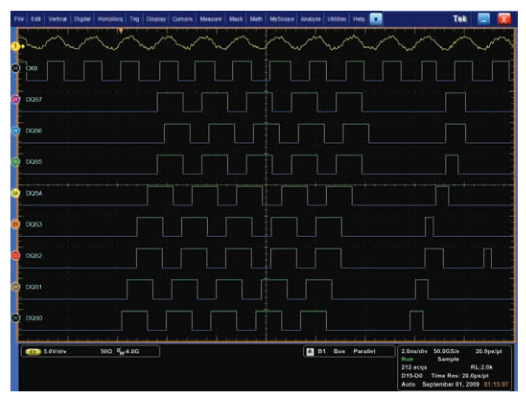

テクトロニクスのMSO70000シリーズ・ミックスド・シグナル・ オシロスコープには、4つのアナログ・チャンネルと16のデジタル・ チャンネルが装備されています。1つまたは2つのデータおよびク ロック・ラインの他、DDRコマンド・バス信号、アドレス・ライン にも接続すると、効果的な測定ができるケースが度々あります。 P6780型プローブは、MSO70000シリーズに接続して使用す る高性能差動プローブです。DDRメモリの検証では、実装密度の 高いレイアウト、小さなパッケージング、信号の接続が大きな課 題となっています。

P6780型ロジック・プローブには豊富な半田付けアクセサリが含 まれているため、さまざまなコネクタ、ピン、デバイス・リード、 配線、ビアに簡単に接続することができます。P6780型の半田付 けプローブ・チップを使用することで、専用のプローブ用フット プリントの必要なしに、必要に応じてテスト・ポイントを追加す ることができます。どのような測定セットアップにおいても、テ スト機器が測定に与える影響が最小限になるように注意を払う必 要があります。P6780型の半田付けチップには、ラインの反射を 低減するためのフェライト・コアが入っています。接続に必要な リード線長を最小限にすることで、優れた信号忠実度を実現して います。

信号の取込み

信号ラインにプローブが接続できたならば、次はメモリ・バスの特定のイベントを検出します。JEDECの適合性測定を実行するためには、リードまたはライト・バーストなど、データ・ストリームの特定の部分のみの測定が必要になります。デバッグにおいては、特定のランク、バンクによる特定のイベント、あるいはシグナル・インテグリティ問題の解析のために、データ依存性のジッタ、タイミング、またはノイズ問題などの特定のデータ・パターンの識別が必要になります。

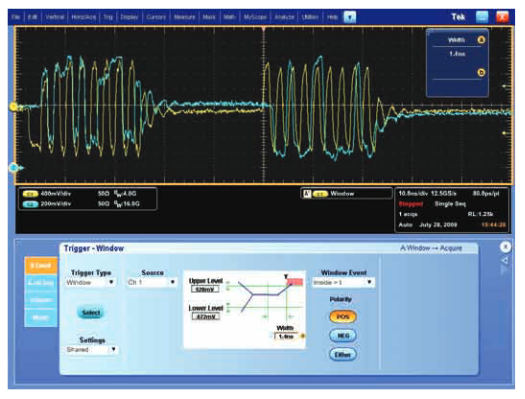

リード・バースト、ライト・バースト、その他のバス・コンディションを識別して分離するにはいくつかの方法があります。最も簡単な方法は、DQS(データ・ストローブ信号)によってリード/バーストの開始点を識別することです。例えば、DDR3では常に書込みの開始はDQSがハイに、読込みの開始はローになります。オシロスコープのハードウェア・トリガは、バーストのプリアンブル部分にトリガでき、リードのみ、またはライトのみを波形の最初の部分に取込むことができます。図7は、ライト・バーストのトリガ・ポイントを中心にして、リードとライトのバーストの両方が表示されています。

MSO/DSA/DPO70000シリーズ・オシロスコープにオプション で搭載されているビジュアル・トリガは、ディスプレイ上でエリ アを定義することで従来のエッジ・トリガを補完でき、DQSバー ストに容易にトリガできます(図8参照)。ディスプレイ上にエリ アを設定することで、このエリアに入るまたは入らないイベント にトリガでき、DQSまたはデータ・ストローブ信号を取込むこと ができます。このエリア形状は、移動したり、回転したり、三角形、 不等辺四角形など4種類が選べ、従来のオシロスコープ・トリガと 組み合わせることで、より正確な信号取込みが可能になります。

| コマンド | SO# | RAS# | CAS# | WE# |

| Mode Register | 0 | 0 | 0 | 0 |

| Refresh | 0 | 0 | 0 | 1 |

| Precharge | 0 | 0 | 1 | 0 |

| Activate Row | 0 | 0 | 1 | 1 |

| Write Column | 0 | 1 | 0 | 0 |

| Read Column | 0 | 1 | 0 | 1 |

| No Operation | 0 | 1 | 1 | 1 |

| Deselect | 1 | X | X | X |

表2. SDRAMコマンド

拡張サーチ/マークによるリード/ライトの識別

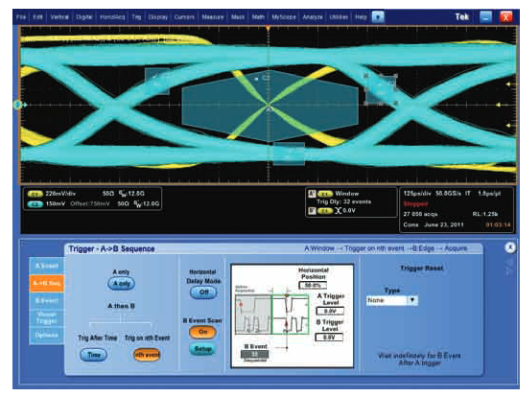

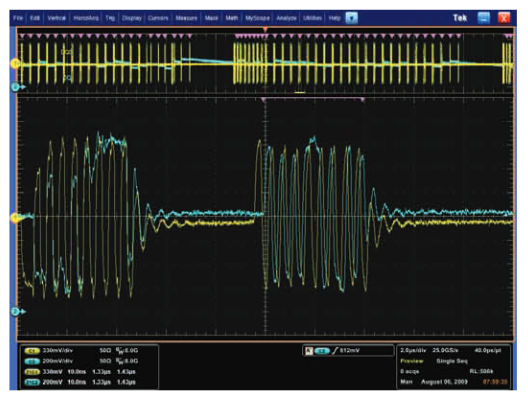

DPO/DSA70000Bシリーズ、MSO70000シリーズのもう1つ の機能に、拡張サーチ/マーク(Opt. ASM:DSA70000Bシリー ズでは標準装備)と呼ばれるソフトウェア・ユーティリティがあ ります。ASM(拡張サーチ/マーク)では、取込んだ波形すべて をスキャンし、設定した条件でサーチします。設定できる条件の 一つにDDRのリード/ライトの識別があります。ASMは取込んだ 波形レコードからすべてのリード・バースト、ライト・バースト を検出し、すべてのバーストにマークを付けます。このマークは 目視による解析にも利用できる他、DDR特有の測定におけるクオ リファイヤとしても利用できるため、データ・ストリームの任意 の部分でのみの測定も可能です。DDRの場合、ASMのサーチ・ア ルゴリズムでは、リード・バーストとライト・バーストでは位相 関係が異なるという性質を利用しています。すなわち、リードで はDQとDQSは同相であり、ライトでは90°ずれます。図9は、す べてのライト・バーストにピンクの三角矢印が波形の上に示され ており、1つのライト・バーストがズーム表示されています。

バスクオリファイ・トリガ

高性能ミックスド・シグナル・オシロスコープには、メモリ・バスのコマンド・ステート、コントロール・ラインを使用して信号を取込む、数多くの機能が用意されています。

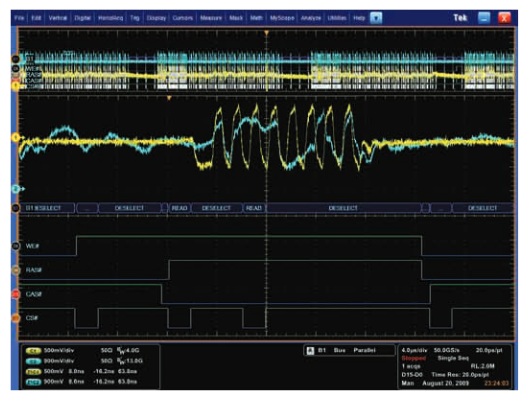

SDRAMのメモリ・コマンドは、メモリ・クロック(CK)の立上りエッジに同期しています。コマンド信号には、チップ・セレクト(S0#またはCS#)、行アドレス・セレクト(RAS#)、列アドレス・セレクト(CAS#)、ライト・イネーブル(WE#)の4つがあります。#は、アクティブ・ロー信号であることを示します(表2を参照)。メモリ・コマンドの検証では、MSOを使用して適切なデータ(DQ)とストローブ(DQS)信号の他に、CK、S0#、RAS#、CAS#、WE#の5つの信号をプロービングする必要があります。MSOのデジタル・チャンネル・メニューで、CK、S0#、RAS#、CAS#、WE#の5つのコマンド信号をプローブ・チャンネルに割り当てます。

ライトまたはリードのコマンド・シーケンスの最初にくるのがActivate Rowコマンドです。MSOでActivate Rowコマンドにトリガするには、MSOのトリガをCommandグループ=0011に設定します。これは、表2によるとS0#=0、RAS#=0、CAS#=1、WE#=1となります。

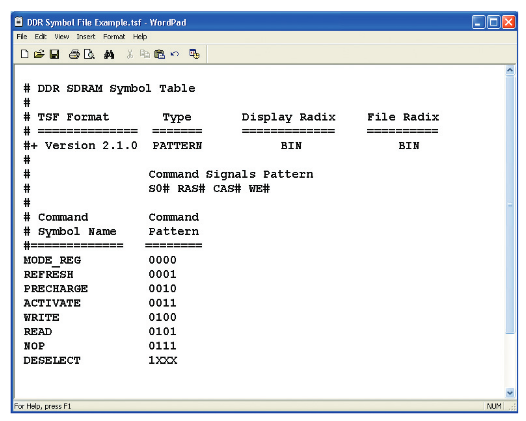

0011などのバイナリの値設定は、操作ミスの原因となりやすいものです。MSOでは、バイナリ、16進、シンボルなど、さまざまなフォーマットに対応します。SDRAMのコマンド・グループなどのロジック・ステートを信号のグループで定義する場合、パターン・シンボル・ファイルを使用します。表2のSDRAMコマンド・テーブルを元に、テクトロニクス・シンボル・ファイル(.tfs)としてMicrosoft Notepadで作成します(図10を参照)。

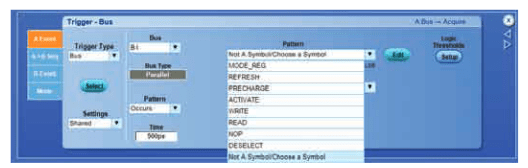

MSOは、Activateコマンドでトリガするために、このパターン・シンボルを使ってトリガを設定します。MSOのバス・トリガ・メニューでパターン・シンボルを使用するには、Bus RadixをSymbolicに変更することでシンボルが選択できるようになります。ビジュアル・トリガと併用することで、DQS、データ・ストローブ、パターン検証など、時間のかかる作業効率が大幅に改善されます。

JEDECに準拠した測定

先にも説明したように、JEDEC仕様ではメモリ技術ごとに適合性測定が規定されています。測定項目としては、クロック・ジッタ、セットアップ/ホールド・タイミング、トランジション電圧、オーバーシュート/アンダーシュート、スルー・レートなどのパラメータ、その他の電気的品質テストが含まれています。規定されているテストの項目数が多いだけでなく、汎用のツールでは測定が複雑なものになります。

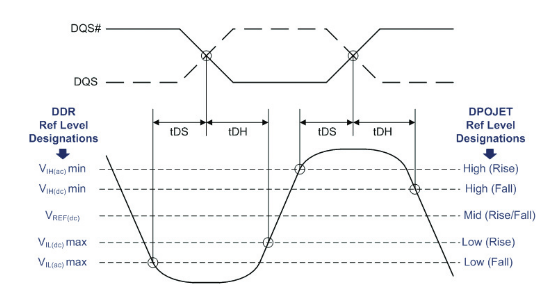

その一例が測定リファレンス・レベルです。JEDECの仕様では、タイミング測定におけるリファレンス電圧レベルが規定されています。図13は、データ信号のタイミング測定で使用されるVihとVilレベル(ACおよびDC)を図示しています。立上りエッジと立下りエッジで使用するレベルが異なっていることにご注意ください。

もう一つの例がスルー・レート測定です。スルー・レートは、データ、ストローブ、コントロール信号で測定する必要があり、セットアップ/ホールドなどのタイミング測定におけるパス/フェイル・リミットの補正のための計算に使用されます。しかし、スルー・レート測定の詳細な方法は、測定する信号によって異なります。図14は一つの測定例ですが、その他のテストでは別な方法が必要であることにご注意ください。

JEDECで規定されている測定方法、リファレンス・レベル、パス/フェイル・リミットなどは複雑であるため、DDRテストなどのアプリケーションに特化した測定ユーティリティがあると非常に便利です。このような測定ユーティリティがあれば、汎用の計測ツールだけでは何時間もかかる測定セットアップが正しく行え、大幅な時間短縮につながります。

DDR解析ソフトウェア

テクトロニクスのリアルタイム・オシロスコープ(DPO/DSA 70000シリーズ、MSO70000シリーズ、DPO7000シリーズ) 用のOpt. DDRAは、DDRデバイスをテストするための専用自動 測定ソフトウェアです。DDRAには、JEDEC規格に準拠した数 多くの測定機能があるだけでなく、規格にないデバイスやシステ ムの実装の測定用にセットアップをカスタマイズできる機能も備 え て い ま す。 現 状 で は、DDR、DDR2、DDR3、LPDDR、 LPDDR2、GDDR3の6種類がサポートされています。

Opt. DDRAは、テクトロニクスのオシロスコープで実行する2種類のソフトウェア・パッケージ(拡張サーチ/マーク(Opt. ASM)とDPOJET(ジッタ/アイ・ダイアグラム解析ソフトウェア)と共に使用することで、強力でありながら使いやすいDDRテスト/デバッグ・ツールとなります。

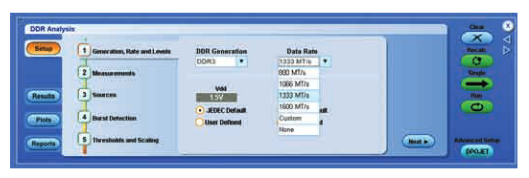

DDRAのメニュー・インタフェースには、選択形式による5つの ステップがあります。インタフェースのステップ1を図15に示し ます。ここでは、テストするDDRの種類(DDR、DDR2など) とメモリのスピードを選択します。この例に示すドロップダウン・ リストには、DDR3で現在利用可能な1600MT/sまでリストさ れています。デフォルトの選択肢の他に独自のスピードを設定す ることができ、オーバークロッキング・アプリケーションなど、 将来の技術革新にもこのソフトウェアによって簡単に対応できま す。DDRの種類とデータ・レートを選択すると、DDRAは測定の ためのリファレンス電圧を自動的に設定します。ここでも「User Defined」が選択でき、JEDECのデフォルトを書き換え、必要に 応じてVdd、Vrefを任意の値に設定することができます。

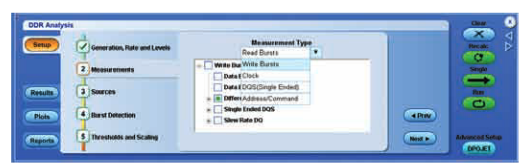

ステップ2では、測定項目を選択します。測定できる項目は、信号 の種類、必要なプロービング接続にまとめられてドロップダウン・ メニューに表示されます。例えば、Clockラインで実行する測定項 目は、Clockドロップダウン・メニューにまとめられています。リー ドに関する測定、ライトに関する測定、アドレス/コマンドに関 する測定も同様にそれぞれのドロップダウン・メニューにまとめ られているため、特定のプローブ接続を必要とするすべての測定 項目が1回でテストできるように選択できます。

DDRAメニュー・インタフェースの残りのステップ3と4では、必要な信号にどのようにプロービングするかが示され、また測定リファレンス・レベルなどのパラメータのカスタム化、調整が行えます。

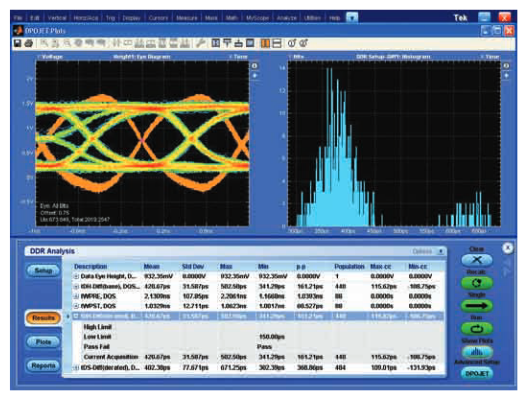

設定を完了して < Run >(または < Single >)を選択すると、オ シロスコープは信号取込みを開始し、データ・バーストを識別し、 必要に応じてマークを付け、選択された測定を実行します。デフォ ルトのメモリ長では約1000UI(Unit Interval)を取込み、すべ ての有効なエッジから測定を行います。データ・バーストの測定 では、自動的にアイ・ダイアグラムを作成してDQとDQSを重ね 書きして相対的なタイミングを示します。DDRAのResultsパネ ルには、統計値、仕様のリミット値、パス/フェイルの結果、そ の他データなど、すべての測定結果が表示されます。必要に応じ て印刷形式のレポートも作成でき、測定で使用した波形データを 保存することもできます。

障害解析とデバッグ

測定結果の元となる取込んだすべての波形データは保持されてい るため、さまざまな利用方法があります。仕様のリミット値から 外れた場合は、波形レコードのどこでフェイルになったかを特定 することができ、特定された領域をズーム表示することでフェイ ル時の信号の詳細とその特性を調べることができます。ソフトウェ アにはさまざまなツールが用意されており、取込んだデータが簡 単に解析でき、注目したい領域をピンポイントで特定することが できます。例えば、図17に示すヒストグラムは全ての測定項目に 適用でき、ワーストケースの測定値を観測することができます(こ の例では、セットアップ時間測定に適用されています)。ヒストグ ラム以外にも様々なプロット表示が利用できます。Cursor Sync というツールでは、プロット上の任意のデータ・ポイントを、対 応する元の波形レコードのイベントとリンクさせることができ、 データのさまざまな部分と表示形式を簡単に切り替えて、より詳 細な解析が行えます。

コマンドとプロトコル動作の検証

SDRAMの書込み動作のプロトコル・シーケンスは、Activateコ マンドで始まり、1つ以上の書込みコマンドが続きます。行アドレ スとバンク・アドレスを持ったActivateコマンドは、読み出し、 書込みのために特定のバンクの特定の行を開きます。列アドレスと バンク・アドレスを持った書込みコマンドは、開かれた特定のバン クの特定の行の指定された列を書き込みのために開きます。開かれ た行がないバンクに書込みコマンドがアクセスした場合は、プロト コル・エラーになります。書込みコマンドの後、メモリは定義され たメモリ・サイクルで、メモリ・コントローラがデータを書き込むことを期待します。開かれた行への書込みが完了した時、他の行を アクセスできるように、開いていた行を閉じる、あるいはプリ チャージ・コマンドでディアクティベートしなくてはなりません。 最もシンプルなDDR2 SDRAMコマンド・プロトコル・シーケン スは、Activate、WriteおよびPrechargeです。連続のwrite-towriteシーケンスは、Activate、複数のWrite、そしてPrecharge です。write-to-readシーケンスは、Activate、Write、Readそ してPrechargeです。開いている行ではWriteとReadの順番は任 意です。メモリ・コントローラが、ある行に2つのWriteコマンドを、 コマンド間にDeselectコマンドを入れることなく連続して送ると DDR2 DRAMプロトコル・エラーとなります。DDR2 DRAMは、 メモリ・コントローラによりストローブされたデータを読むことで Writeコマンドに応答します。

DRAMのもう一つの重要な仕様が、Prechargeコマンドが送られた後、行を開くためにActivateコマンドが送られる前の最小tRP時間です。PrechargeコマンドにトリガするようにMSOのトリガを設定し、Prechargeコマンドと同じバンクのActivateコマンド間のtRP時間を測定することで簡単に検証できます。

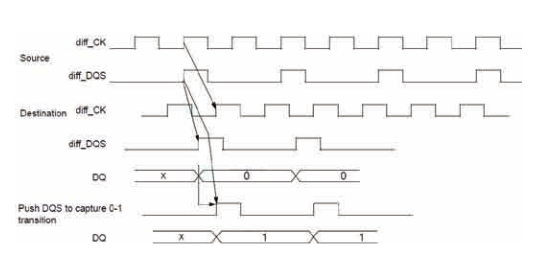

同様のプロトコル/タイミング検証技術は、DDR3 DRAMの読み出し/書込み動作にも適用されます。しかし、DDR3の複数の連続した書込み動作は仕様で認められている点に注意が必要です。バス・トラフィックの解析において、書込みバーストを分離する時に、ストローブ信号の終端ロジックが考慮されないと、連続したストローブでは2つの連続した書込みを1つの書き込みバーストとみなしてしまいかねません。

読み出しまたは書込みサイクル動作の検証が終わったならば、次のような項目を検証する必要があります。

基本機能テスト

プロトタイプのシステム初期化では、クロック、リセット、PLLラインをチェックすることで、他のサブシステムに影響を及ぼす重要な問題を検出するのに役立ちます。ブラウザまたはハンドヘルド・タイプのプローブは、測定ポイントを切り替えながら重要な信号をチェックするのに適しています。

もう一つの基本テスト・チェックが波形インピーダンスの検証で す。SDRAMメモリ・システムではシングルエンド信号、差動信 号が使用されるため、これらの信号波形は異なったインピーダン スになります。この検証には、DSA8200型サンプリング・オシ ロスコープとTDR(Time Domain Reflectometer)サンプリン グ・モジュールを使用します。インピーダンスやターミネーション に不具合があると、なめらかでない立上り/立下りエッジなど、 良質なエッジ品質が得られません。エッジ品質が悪いと、信号ト ランジションが長くなり、クロック信号の有効なデータ・ウィン ドウが減少します。

パワー・マネジメントと特殊な動作モード

バスがパワー・ステートに入ったり、出たりすると、ラインによっ ては非アクティブまたは再度アクティブになるものがあります。 追加的なこのステートの変化によりシステムのインターオペラビ リティが複雑になるため、注意が必要です。例えば、LPDDR2(Low Power DDR2)では、Partial Array Self Refreshなどの優れた パワー・マネジメント技術を採用しており、メモリ・アレイの必 要な部分のみが使用されるため、効率と低消費電力性に優れてい ます。

書込み/読み出しレベリング

データ・レートのスピード・アップのみだと、ソース・シンクロ ナス・バスの帯域拡張は難しくなってきています。しかし、最先 端の物理レイヤ設計技術によって広帯域化が可能になります。 DDR3はフライバイ・トポロジをサポートしており、メモリ・コン トローラからの信号(コマンド、アドレスおよびクロック)は一 筆書き的にシーケンシャルに各メモリ・コンポーネントに届くた め、負荷を低減し、全体としてのシグナル・インテグリティが向 上します。各コンポーネント間のフライト・タイムによる電気的 遅延のため、メモリ・コントローラはクロック(CK)と各コンポー ネントのデータ・ストローブ(DQS)を合わせるための遅延校正 が必要になります。この動作により、クロックとストローブ信号 間のフライト・タイム・スキューが低減され、メモリ・システム のマージンに余裕が生まれます。

DQ/DQS のマージニング

先にも説明したように、JEDECは規格適合性のための数多くの測 定を規定しています。半導体およびコンポーネントの設計エンジ ニアは、さまざまなプロセス、電圧、温度における設計の特性を 理解するため、基本的なパラメータ・テストの検証より先を見据 えています。代表的な例として、ノイズに対する耐性と感度の確 認のために、VrefまたはVddラインを変化させた時のデータ(DQ) とストローブ(DQS)をモニタします。これにより、広範囲な動 作条件でもデバイスが正しく動作することを確認することができ ます。

デジタルとアナログ表示の組み合わせ

先にも説明したように、DDR信号の接続には、インターポーザや 半田付けプローブ・チップなど、さまざまな方法があります。数 多くのデジタル・ラインをモニタする必要がある場合に、シグナル・ インテグリティ関連の問題が発覚した後で、別のアナログ用プロー ブを追加接続して信号を観測する、というのはあまり一般的では ありません。これは「ダブル・プロービング」として知られており、 信号のインピーダンス環境の妥協が必要になります。2本のプロー ブを同時に使用すると信号に負荷を加えることになり、デバイス の立上り時間、立下り時間、振幅、ノイズ性能が低下することに なります。

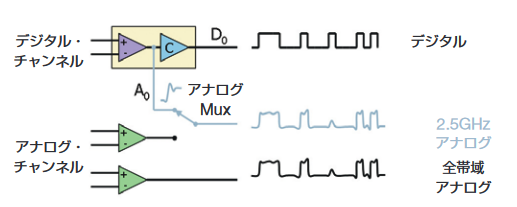

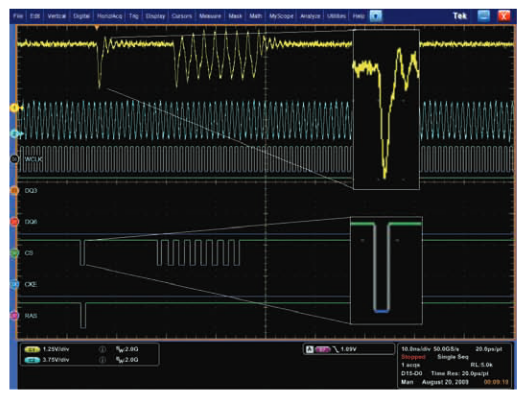

MSO70000シリーズのiCapture機能により、余分な負荷容量を 加えることなく、またダブル・プロービングをするためのセット アップ時間の必要なしに、デジタルとアナログの振る舞いを時間 相関を取りながら観測できます。16のデジタル・チャンネルの任 意のチャンネルをオシロスコープのアナログ信号入力経路にマル チプレクスできるため、注目したい信号のデジタルとアナログ波 形を並べて表示することができます。図22は、GDDR5回路にお けるチップ・セレクト・ラインの検証の様子を示しています。デ ジタル・データのサンプリングで使用されているロジック・スレッ ショルドを確認したり、高い精度でのシグナル・インテグリティ を検証できます。

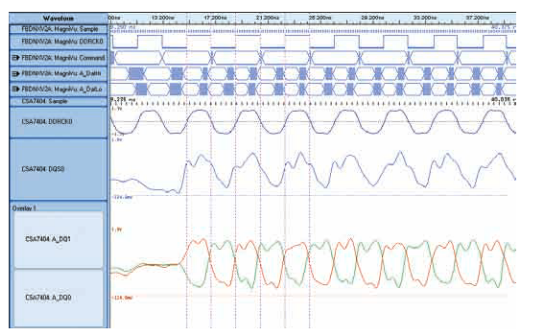

20チャンネル以上のシステム・ステート・モニタリングが必要な場合は、TLA7000シリーズのiCapture機能を使用することで、100チャンネル以上のデジタル信号の動きを観測することができます。図23に示すように、ロジック・アナライザのディスプレイ上に、取込んだデジタル信号とオシロスコープで取込んだ4つのアナログ・チャンネルが、同じディスプレイ上に表示できます。

まとめ

このアプリケーション・ノートでは、DDRテストに関する多くの 課題と、メモリ設計の検証/デバッグに必要な計測ツールについ て説明しました。当社は、高性能ミックスド・シグナル・オシロ スコープ、真の差動TDR、Nexus Technology社のメモリ・サポー トとロジック・アナライザを初めとする幅広いツール・セットを 提供し、組込みシステム、コンピュータ設計エンジニアのための DDRベース・メモリ設計の正確な電気的テストと動作評価がすば やく、正確に行えます。DDRテストの詳細については、JEDEC のウェブ・サイト(www.jedec.org)またはMemory Implemen ters Forumのウェブ・サイト(www.memforum.org)をご参照 ください。DDR仕様の詳細、ホワイト・ペーパ、その他の資料が 用意されています。また、DDRのテストについては、テクトロニ クスのウェブ・サイト(www.tektronix.com/ja/memory)もご 参照ください。豊富なアプリケーション・ノート、ウェブ・セミナ、 推奨機器リストなどがご覧いただけます。