Contact us

Live Chat with Tek representatives. Available 6:00 AM - 4:30 PM

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

Có được góc nhìn chuyên sâu hơn về thời gian trên nhiều ứng dụng với phần mềm Phân tích Jitter Nâng cao (tùy chọn DJA). Có sẵn trên các dòng máy hiện sóng 5 Series B MSO, 6 Series B MSO và 7 Series DPO, DJA mang đến khả năng phân tích jitter, biểu đồ mắt và phân tích thời gian mạnh mẽ, từ xung nhịp nhúng tốc độ thấp cho đến các giao diện nối tiếp tốc độ cao.Từ liên kết nối tiếp đến xung nhịp và PLL, DJA giúp bạn phát hiện nguồn gốc jitter, gỡ lỗi nhanh hơn và xác thực hiệu năng với độ tin cậy cao.

Tìm hiểu:

- Phân tích Jitter cho quy trình xác thực và gỡ lỗi

- Làm thế nào để xác định và khắc phục các vấn đề về Jitter

- Cách tách jitter tổng thể thành các thành phần để phân tích nguyên nhân gốc rễ

- Các công cụ trực quan hóa hàng đầu trong ngành để gỡ lỗi vấn đề jitter và xác thực độ toàn vẹn tín hiệu

- Cách các kết quả jitter của Tektronix được xây dựng dựa trên các tiêu chuẩn ngành.

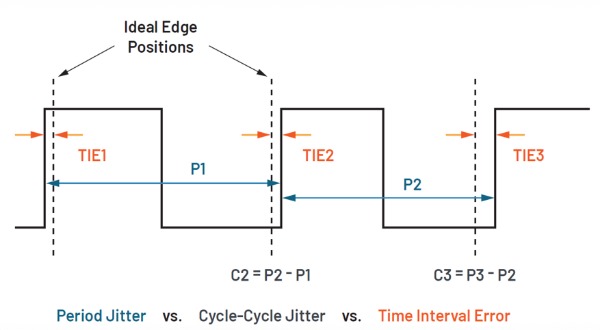

Các phép đo jitter cơ bản khác nhau

Phân tích Jitter cho quy trình xác thực và gỡ lỗi

Jitter là sự biến thiên không mong muốn trong thời gian của tín hiệu, làm suy giảm độ toàn vẹn tín hiệu.Trong các hệ thống tốc độ cao, ngay cả những dịch chuyển thời gian nhỏ cũng có thể làm sụp biểu đồ mắt, gây lỗi bit và khiến thiết kế vượt ngoài thông số kỹ thuật.ù xuất phát từ nhiễu nguồn, xuyên âm, phản xạ hay sự bất ổn của xung nhịp, jitter đều đe dọa các thiết kế USB, PCIe, DDR và Ethernet—ảnh hưởng đến hiệu năng cũng như độ tin cậy.

Cách nhận biết và khắc phục các vấn đề về jitter

Nếu bạn thấy hiện tượng biểu đồ mắt bị đóng, lỗi dữ liệu hoặc sự cố xung nhịp, thì phân tích jitter không còn là tùy chọn—mà là bắt buộc. Tektronix cung cấp các công cụ chính xác như biểu đồ mắt, đồ thị TIE và phân tách jitter để xác định nguyên nhân gốc rễ và đảm bảo biên độ thời gian được đáp ứng.

Cách phân tích và gỡ lỗi Jitter:

- Thu nhận tín hiệu DUT bằng máy hiện sóng có băng thông phù hợp và đầu dò tương ứng

- Thực hiện phân tích jitter chỉ với vài cú nhấp chuột bằng phần mềm DJA (tùy chọn DJA)

- Cấu hình phục hồi xung nhịp để mô phỏng hành vi của hệ thống đang được kiểm thử.

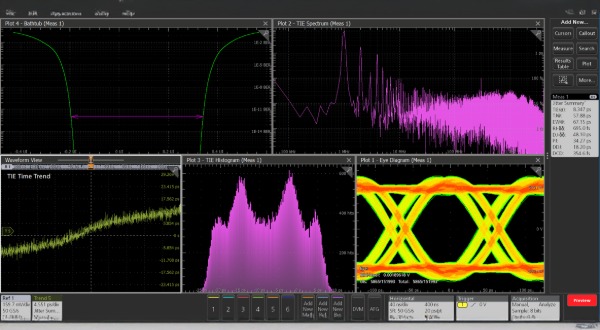

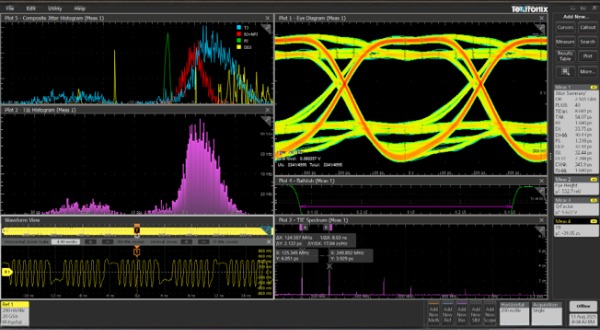

- Thực hiện phân tích TIE, biểu đồ mắt, bồn tắm jitter và phân tích phổ.

- Phân tích jitter tổng

- Liên kết jitter với các nguyên nhân gốc có khả năng xảy ra.

- Thực hiện các sửa chữa và kiểm tra lại

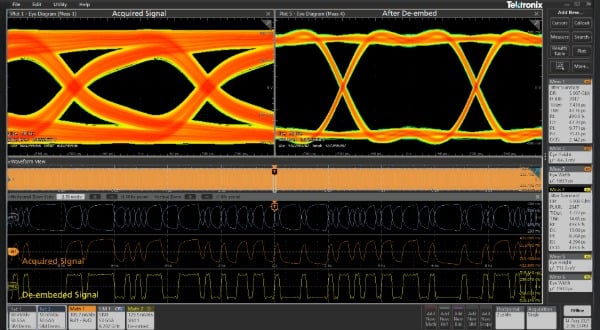

- Bỏ nhúng, nhúng hoặc sử dụng cân bằng bằng phần mềm SIM (opt.SIM).

- Điều chỉnh EQ, bố cục, công suất hoặc lựa chọn linh kiện

- Thu thập lại và phân tích lại để xác nhận cải thiện

- Ghi chép mọi thứ để đảm bảo khả năng truy xuất nguồn gốc và tuân thủ quy định

Phân tích jitter cho thấy một liên kết 2,5 Gb/s có jitter tuần hoàn chiếm ưu thế ở khoảng 125 MHz, DDJ đáng kể do ISI và DCD có thể đo được—cho thấy nguyên nhân gốc rễ có khả năng đến từ xung nhịp hoặc ghép nối nguồn điện.

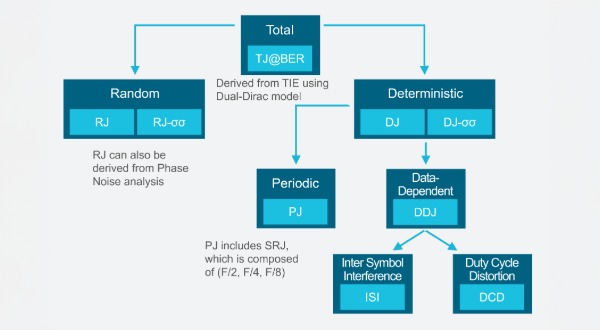

Phân tách Jitter Tổng thể thành các thành phần gốc

Phân tách jitter giúp xác định nguyên nhân gốc rễ và áp dụng các biện pháp khắc phục cụ thể—như tối ưu hóa nguồn xung nhịp, điều chỉnh cân bằng tín hiệu hoặc cải thiện bố cục mạch.

Phần mềm Phân tích Jitter Nâng cao (tùy chọn DJA)của Tektronix giúp bạn tách biệt jitter.Chỉ với vài thao tác nhấp chuột, bạn có thể xác định Jitter Tổng thể (TJ) thông qua phân tích chi tiết các yếu tố sau:

- Jitter ngẫu nhiên (RJ): Giống như nhiễu, không bị giới hạn

- Jitter xác định (DJ): Có thể dự đoán trước, có giới hạn (như jitter định kỳ)

- Và các thành phần phụ (PJ, DDJ, ISI, DCD, v.v.)

Công cụ trực quan hóa dẫn đầu ngành

Phần mềm phân tích jitter tiên tiến của Tektronix (tùy chọn DJA) được thiết kế để cung cấp cho bạn cái nhìn sâu sắc về hành vi của tín hiệu.

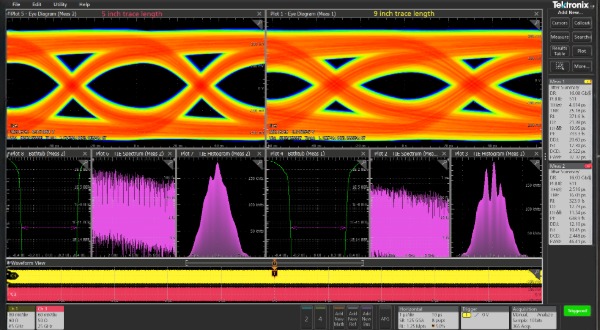

- Tektronix hỗ trợ độc quyền gần như không giới hạn các phép đo và đồ thị song song—mỗi phép đo có cài đặt phục hồi xung nhịp độc lập—để so sánh nhanh song song các chiến lược cân bằng tín hiệu, độ nhạy biên hoặc thay đổi cấu hình.

- Nhiều đồ thị tương tác—bao gồm biểu đồ mắt, biểu đồ tần suất, đường cong bồn tắm, phổ và nhiều loại khác—được hiển thị trong một giao diện tích hợp duy nhất để mang lại góc nhìn sâu hơn.

- Kết xuất biểu đồ mắt theo thời gian thực để hiển thị đồng thời sai lệch thời gian, nhiễu và méo dạng, với khả năng mô phỏng PLL do người dùng tự định nghĩa.

- Các chỉ số biểu đồ mắt như Chiều cao mắt (Eye Height), Chiều rộng mắt (Eye Width), Eye@BER, Eye High/Low và Hệ số Q (Q-Factor) giúp định lượng biên độ tín hiệu và hỗ trợ phân tích dự đoán BER.

- Kiểm thử mặt nạ mắt toàn diện, bao gồm tính năng tự động căn chỉnh và trực quan hóa biên độ, nhằm xác thực tuân thủ tiêu chuẩn trên nhiều chuẩn nối tiếp khác nhau.

Khám phá phần mềm máy hiện sóng phân tích jitter nâng cao (DJA)

So sánh nhanh song song giữa đường mạch 5 inch và 9 inch

Phân tích phương sai độ trễ đáng tin cậy, dựa trên các tiêu chuẩn ngành

Các công cụ phân tích jitter, biểu đồ mắt và thời gian của Tektronix được phát triển dựa trên những đổi mới cốt lõi đã định hình nên ngành công nghiệp — được hỗ trợ bởi các kỹ thuật được cấp bằng sáng chế như phục hồi xung nhịp thời gian thực, kết xuất biểu đồ mắt và phân tách jitter dựa trên phổ.Được tin cậy và chứng nhận bởi PCI-SIG, USB và các tổ chức hàng đầu khác trong ngành.

Các phép đo jitter và thời gian của Tektronix được xây dựng trên cùng những thuật toán đã được kiểm chứng, vốn được sử dụng trong phần mềm DPOJETtiêu chuẩn ngành—đảm bảo tính nhất quán, độ tin cậy và sự quen thuộc cho những người dùng lâu năm.

Tính tương quan được xác thực thường xuyên thông qua việc tham gia các sự kiện plugfest, hội thảo tuân thủ và các bài kiểm thử so sánh nội bộ — giúp đảm bảo kết quả của chúng tôi phù hợp với các phương pháp và kỳ vọng của ngành.