연락처

텍트로닉스 담당자와 실시간 상담 6:00am-4:30pm PST에 이용 가능

전화 문의

9:00am-6:00PM KST에 이용 가능

다운로드

매뉴얼, 데이터 시트, 소프트웨어 등을 다운로드할 수 있습니다.

피드백

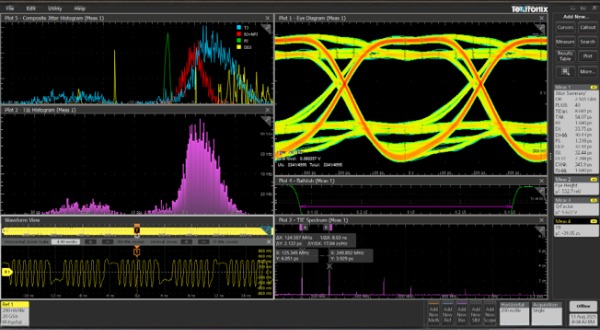

고급 지터 분석 소프트웨어(옵션 DJA)를 통해 다양한 응용 분야에서 심층적인 타이밍 인사이트를 얻으세요. 5 시리즈 B MSO, 6 시리즈 B MSO 및 7 시리즈 DPO 오실로스코프에서 사용할 수 있는 DJA는 저속 임베디드 클록에서 고속 직렬 인터페이스에 이르기까지 강력한 지터, 아이 다이어그램 및 타이밍 분석을 제공합니다. 직렬 링크에서 클럭 및 PLL에 이르기까지 DJA는 지터 소스를 발견하고, 더 빠르게 디버깅하며, 자신 있게 성능을 검증할 수 있도록 도와줍니다.

다양하고 근본적인 지터 측정

검증 및 디버그 워크플로우를 위한 지터 분석

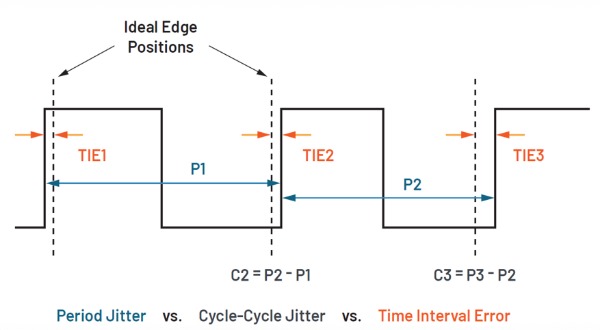

지터는 신호 타이밍에서 생기는 변화로, 신호 무결성을 손상시킵니다. 고속 시스템에서는 미세한 타이밍 변화로도 아이다이어그램이 붕괴되고 비트 오류가 발생하며 설계가 사양을 벗어날 수 있습니다. 전력 노이즈, 크로스토크, 반사 또는 클럭 불안정으로 인해 발생하는 지터는 USB, PCIe, DDR 및 이더넷 설계를 위협하여 성능과 신뢰성에 영향을 미칩니다.

지터 문제를 식별하고 해결하는 방법

아이 클로저, 데이터 오류 또는 클럭 문제가 발생하면 지터 분석은 선택이 아닌 필수입니다. Tektronix는 아이 다이어그램, TIE 플롯, 지터 분해와 같은 정밀한 도구를 제공하여 근본 원인을 파악하고 타이밍 마진을 보장합니다.

지터를 분석하고 디버그하는 방법:

- 적절한 오실로스코프 대역폭과 프로브를 사용하여 DUT 신호를 획득하세요.

- DJA 소프트웨어(옵션 DJA)를 사용하여 몇 번만 클릭하여 지터 분석을 실행하세요.

- 테스트 중인 시스템의 동작을 모방하도록 클럭 복구를 구성합니다.

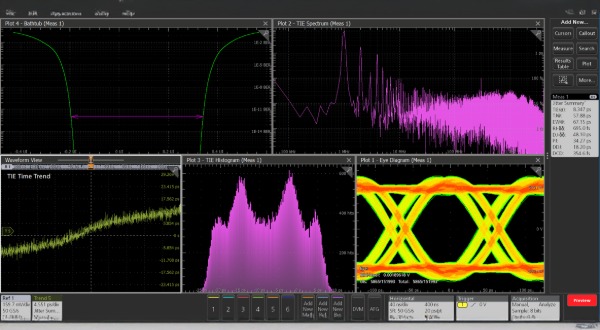

- TIE, 아이 다이어그램, 지터 배스텁(jitter bathtub) 및 스펙트럼 분석을 수행합니다.

- 전체 지터를 분해합니다.

- 지터와 가능한 근본 원인의 상관 관계를 파악하세요.

- 수정 사항을 적용하고 다시 테스트하세요.

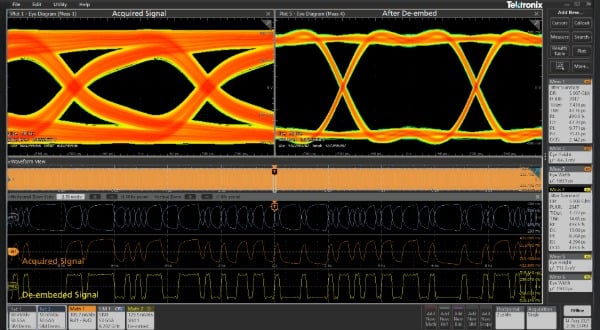

- SIM 소프트웨어(옵션 SIM)를사용하여 디임베드, 임베드 또는 이퀄라이제이션을 수행합니다.

- EQ, 레이아웃, 전원 또는 구성 요소 선택을 조정합니다.

- 개선 여부를 확인하기 위해 데이터를 다시 수집하고 재분석합니다.

- 추적 가능성과 규정 준수를 위해 모든 내용을 문서화하세요.

지터 분석 결과, 2.5Gb/s 링크에서 ~125MHz의 주기적 지터가 지배적이며, ISI로 인한 상당한 DDJ와 측정 가능한 DCD가 발견되었습니다. 이는 클럭 또는 전원 공급 장치 커플링이 근본 원인일 가능성을 시사합니다.

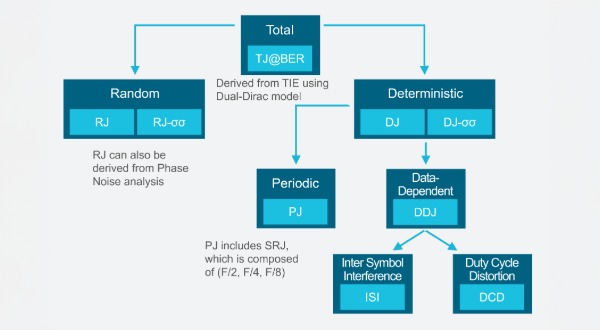

전체 지터를 근본적인 구성 요소로 분해하기

지터 분해는 근본 원인을 식별하고, 클럭 소스의 최적화, 이퀄라이제이션의 조정 또는 레이아웃 개선 등의 특정 수정 사항을 적용하는 데 도움이 됩니다.

Tektronix Advanced Jitter Analysis(옵션 DJA) 소프트웨어는 지터를 격리하는 데 도움이 됩니다. 몇 번만 클릭하면 다음과 같은 상세 분석을 통해 전체 지터(TJ)를 결정할 수 있습니다.

- 랜덤 지터(RJ): 노이즈와 유사하며 제한 없음

- 결정적 지터(DJ): 예측 가능하고 제한적임(주기적 지터와 유사함)

- 하위 구성 요소(PJ, DDJ, ISI, DCD 등)

업계 최고의 시각화 도구

Tektronix의 고급 지터 분석 소프트웨어(옵션 DJA)는 신호 동작에 대한 심층적인 인사이트를 제공하도록 설계되었습니다.

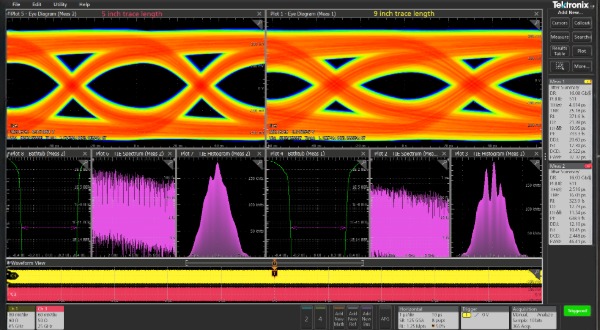

- Tektronix는 각각 독립적인 클록 복구 설정을 갖춘 사실상 무제한의 병렬 측정 및 플롯을 독보적으로 지원하여, 이퀄라이제이션 전략, 마진 감도 또는 구성 변경 사항을 신속하게 비교할 수 있습니다.

- 아이다이어그램, 히스토그램, 배스텁 곡선(bathtub curve), 스펙트럼 등 다양한 대화형 플롯을 하나의 통합된 UI에서 제공하여 더 나은 인사이트를 얻을 수 있습니다.

- 사용자 정의 가능한 PLL 에뮬레이션을 통해 실시간 아이 다이어그램 렌더링이 타이밍, 노이즈, 왜곡을 한 번에 보여줍니다.

- 아이 다이어그램 지표인 아이 높이, 아이 너비, Eye@BER, 아이 하이/로우, Q-인자를 통해 신호 마진을 정량화하고 예측 BER 분석을 수행할 수 있습니다.

- 자동 맞춤 및 여백 시각화를 포함한 포괄적인 아이 마스크 테스트는 광범위한 직렬 표준에 대한 표준 준수 검증을 제공합니다.

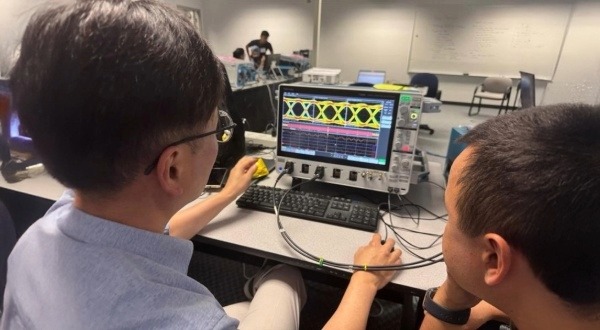

5인치 트레이스와 9인치 트레이스의 빠른 병렬 비교

업계 표준에 기반한 신뢰할 수 있는 지터 분석

Tektronix 지터, 아이 다이어그램 및 타이밍 분석 도구는 업계를 정의한 동일한 핵심 혁신을 바탕으로 설계되었습니다. 특허 받은 실시간 클록 복구, 아이 렌더링 및 스펙트럼 기반 지터 분해 기술이 이를 뒷받침합니다. PCI-SIG, USB 및 기타 주요 업계 기관의 신뢰와 인증을 받았습니다.

Tektronix 지터 및 타이밍 측정은 업계 표준 DPOJET 소프트웨어에서 사용되는 검증된 동일한 알고리즘을 기반으로 하여, 장기 사용자에게 일관성, 신뢰성 및 연속성을 보장합니다.

PlugFest, 적합성 워크숍, 내부 비교 테스트에 참여하여 상관관계를 정기적으로 검증하고 있으며, 이를 통해 당사의 결과가 업계의 방법 및 기대치에 부합하는지 확인하고 있습니다.