Contactez-nous

Chat en direct avec un représentant Tek. Service disponible de 9 h à 17 h, CET jours ouvrables.

Appelez-nous au

Disponible de 9 h à 17 h CET jours ouvrables.

Télécharger

Télécharger des manuels, des fiches techniques, des logiciels, etc. :

Feedback

Obtenez des informations plus approfondies sur le timing dans un large éventail d'applications avec le logiciel Advanced Jitter Analysis (opt. DJA). Disponible sur les oscilloscopes MSO Série 5 B, MSO Série 6 B et DPO Série 7, DJA offre une analyse puissante de la gigue, du diagramme de l'œil et de la synchronisation pour tout type d'application, des horloges embarquées à faible vitesse aux interfaces série à haut débit. Qu'il s'agisse de liaisons série, d'horloges ou de PLL, DJA vous aide à découvrir les sources de gigue, à déboguer plus rapidement et à valider les performances en toute confiance.

Découvrez :

- Analyse de gigue pour les flux de travail de validation et de débogage

- Comment identifier et résoudre les problèmes de gigue

- Comment décomposer la gigue totale en ses composants pour une analyse des causes profondes

- Outils de visualisation de pointe pour déboguer les problèmes de gigue et valider l'intégrité du signal

- Comment les résultats de gigue de Tektronix sont fondés sur les normes du secteur

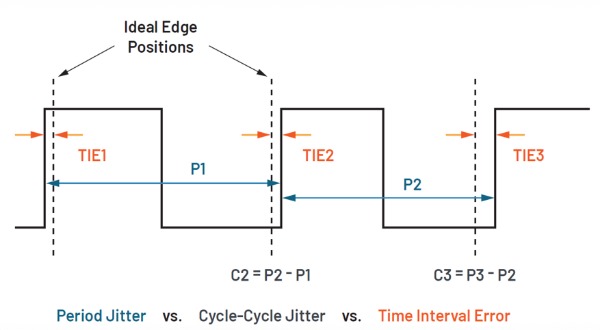

Différentes mesures fondamentales de gigue

Analyse de la gigue pour les flux de travail de validation et de débogage

La gigue est la variation non désirée de la synchronisation du signal, qui nuit à l'intégrité du signal. Dans les systèmes à haut débit, même des décalages de synchronisation subtils peuvent perturber les diagrammes de œil, introduire des erreurs de bits et rendre les conceptions non conformes aux spécifications. Qu'il s'agisse de bruits d'alimentation, de diaphonie, de réflexions ou d'instabilité de l'horloge, la gigue menace vos conceptions USB, PCIe, DDR et Ethernet, impactant les performances et la fiabilité.

Comment identifier et résoudre les problèmes de gigue

Si vous constatez une fermeture de l'œil, des erreurs de données ou des problèmes d'horloge, l'analyse de la gigue n'est pas facultative, elle est essentielle. Tektronix propose des outils précis tels que des diagrammes de l'œil, des tracés TIE et la décomposition de la gigue pour isoler la cause profonde et garantir le respect des marges de synchronisation.

Comment analyser et déboguer la gigue :

- 3. Acquérez le signal DUT avec une bande passante d'oscilloscope et une sonde adéquates

- Effectuez une analyse de gigue en quelques clics grâce au logiciel DJA (opt. DJA)

- Configurer la récupération de l'horloge pour reproduire le comportement du système testé

- Effectuez une analyse TIE, un diagramme de l'œil, une courbe de gigue et une analyse du spectre.

- Décomposez la gigue totale

- Établissez une corrélation entre la gigue et les causes profondes probables

- Apportez des correctifs et tester à nouveau

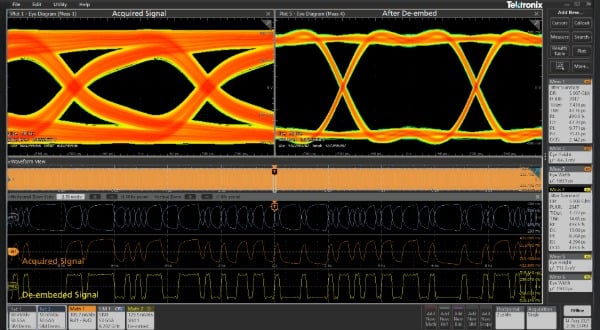

- Désembarquez, embarquez ou utilisez l'égalisation à l'aide du logiciel SIM (opt.SIM)

- Ajustez l'égalisation, la disposition, la puissance ou la sélection des composants

- Réacquérez et réanalysez pour confirmer l'amélioration

- Tout documenter pour assurer la traçabilité et la conformité

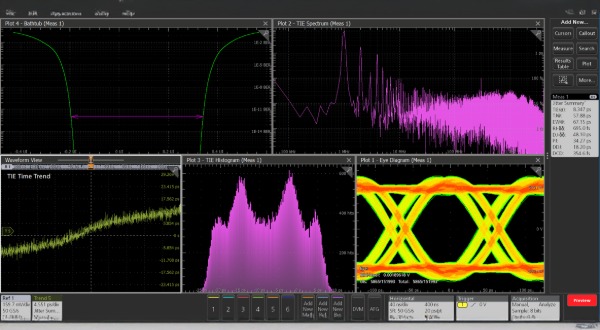

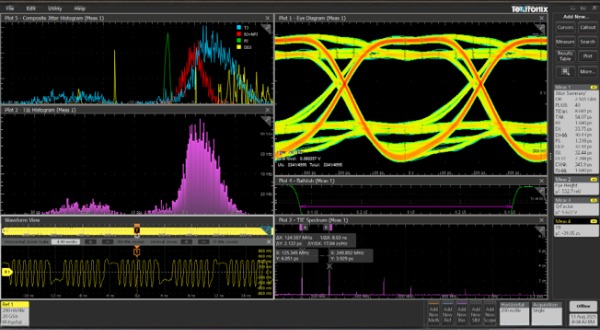

L'analyse de la gigue révèle une liaison de 2,5 Gb/s avec une gigue périodique dominante à ~125 MHz, une DDJ significative de l'ISI et un DCD mesurable, ce qui indique que le couplage de l'horloge ou de l'alimentation est probablement à l'origine du problème.

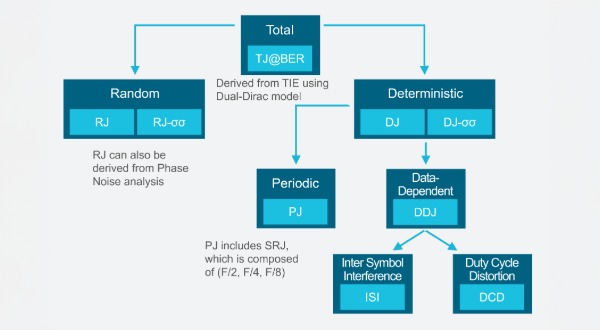

Décomposer la gigue totale en ses composantes fondamentales

La décomposition de la gigue permet d'identifier les causes profondes et d'appliquer des correctifs ciblés, comme l'optimisation des sources d'horloge, l'ajustement de l'égalisation ou l'amélioration de la configuration.

Le logiciel Advanced Jitter Analysis de Tektronix (opt. DJA) vous aide à isoler la gigue. En quelques clics, déterminez la gigue totale (TJ) grâce à une analyse détaillée des éléments suivants :

- Gigue aléatoire (RJ) : semblable à du bruit, sans limite

- Gigue déterministe (DJ) : prévisible, limitée (comme la gigue périodique)

- Et les sous-composants (PJ, DDJ, ISI, DCD, etc.)

En savoir plus sur l'isolation, l'analyse et le traitement de la gigue

Outils de visualisation de pointe

Le logiciel Advanced Jitter Analysis de Tektronix (opt. DJA) est conçu pour vous offrir une compréhension approfondie du comportement des signaux.

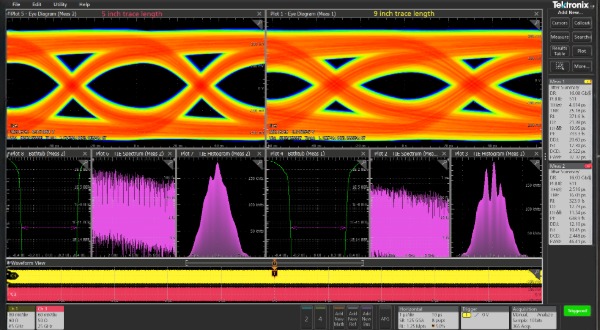

- Tektronix prend en charge de manière unique des mesures et des tracés parallèles pratiquement illimités, chacun avec des paramètres de récupération d'horloge indépendants, pour des comparaisons rapides côte à côte des stratégies d'égalisation, de la sensibilité des marges ou des changements de configuration.

- Plusieurs tracés interactifs (diagramme de l’œil, histogramme, courbe en baignoire, spectre, et bien plus encore) au sein d'une interface utilisateur unique et intégrée pour une meilleure compréhension.

- Rendu en temps réel du diagramme de l'œil pour révéler la synchronisation, le bruit et la distorsion avec une émulation PLL définissable par l'utilisateur, le tout en même temps.

- Mesures du diagramme de l'œil comme la hauteur de l'œil, la largeur de l'œil, l'œil@BER, l'œil haut/bas et le facteur Q pour quantifier la marge du signal et permettre une analyse prédictive du BER.

- Test complet du masque de l'œil, y compris l'ajustement automatique et la visualisation de la marge, pour une validation conforme aux normes sur une large gamme de normes série.

Découvrez le logiciel d'oscilloscope Advanced Jitter Analysis (DJA)

Comparaison rapide côte à côte d'une trace de 5 pouces et de 9 pouces

Analyse fiable de la gigue, basée sur les normes de l'industrie

Les outils d'analyse de gigue, de diagramme de l'œil et de synchronisation de Tektronix sont conçus avec les mêmes innovations fondamentales qui ont défini l'industrie, soutenues par des techniques brevetées de récupération d'horloge en temps réel, de rendu de l'œil et de décomposition de la gigue basée sur le spectre. Reconnu et certifié par PCI-SIG, USB et d'autres organismes industriels de premier plan.

Les mesures de gigue et de synchronisation de Tektronix sont basées sur les mêmes algorithmes éprouvés que ceux utilisés dans notre logiciel DPOJET standard, ce qui garantit la cohérence, la confiance et la continuité pour les utilisateurs de longue date.

La corrélation est régulièrement validée par la participation à des plugfests, des ateliers de conformité et des tests de comparaison internes, ce qui contribue à garantir que nos résultats correspondent aux méthodes et aux attentes du secteur.

Ressources