Introduction

The Semiconductor Industry is always searching for new special materials, dielectric solutions, and new device geometries for scaling down the device size further and further. Lateral and vertical heterostructures of 2D materials, for instance, have led to new revolutionary tiny and low-power electronics.

A 4200A Electrical Parameter Characterization system controlled from his touchscreen display

Researchers, scientists, and engineers in the industry all share a common headache when producing an accurate report of the electrical characteristics of semiconductor devices like special NANO-FETs. This headache becomes even worse when they need to prove they can actually control these parameters in an easy and repeatable way.

It’s the typical problem of electrical characterization in the low current range: the need to identify the attainable device performance under different conditions for low power/low leakage current MOSFETs.

Measurements are critical since they identify the specific figures of merit (FoM) that confirm or deny the effective behavior within specific applications.

For instance, n-type FETs require evaluating on and off drain currents at different values of source, drain, and gate voltages. FoMs can vary across applications, but the way to obtain them is essentially common: something sources a precise and controlled level of voltage or current that varies in a certain way, while voltage and current measurements are also accurately taken to be correlated with each specific variable variation.

The problem is practically solved by using a certain number of source measure units (SMUs) – special instruments capable of sourcing current or voltage while measuring both current and voltage.

But wherever a practical solution seems readily available, a lot of hidden “details” may cause failures and misleading results. Let’s explore them.

A critical question you should ask yourself

More and more often, engineers fall into the trap of forgetting to carefully look holistically into their test system. Or better, they clearly see their device, and they clearly see their instruments, but they fail to see what’s in between.

For instance, I have often seen oscilloscope users forgetting that they were using probes to reach the specific test point to measure on their circuit board.

Those who were reminded to consider the effect of the probe on signals still tended to forget about the probe lead’s effect on the measurement, as well as problems related to signal coupling.

“Come on, does it really matter?” they asked. Everything does, unfortunately. And we need to take this into account.

For DC characterization applications the risk is similar. Even if the physical probing on the device is essentially left to a complex and expensive probe station system, the SMUs that have to force the voltage and measure the current are connected to the probe card by means of cables.

Does that mean we should consider cables as potentially affecting our measurements results?

Regardless of the answer, what matters is that you always ask this question to yourself before proceeding. And more importantly, make sure that your answer is correct.

Precision measurements in CMOS manufacturing are a typical example where connectivity matters.

Connectivity, in fact, means capacitances to be added to the test system. And since today’s MOSFETs are characterized over a wider extended frequency range, any effect from added capacitances must be carefully considered.

Let’s look first into the connectivity contribution to capacitance; parametric (automated) test equipment generally uses triax cable connections, a very typical example of a low noise connection between the source and measure test units and the device under test.

Triax cables are a sort of special coaxial cable that also insulate the part conducting signals by means of an extra outer copper Faraday shield. Even if the Faraday shield reduces the cable’s distributed capacitance, when the total length of the cable becomes significative the cable’s added capacitance can affect your measurements.

Let’s consider a real use case when a test system has to characterize n-MOSFET transistors for instance. In this application, a test system based on SMUs is used to trace the so called I-V curves, sometimes referred to as the “Output characteristic” or also the “Transfer characteristics.”

The gate voltage is programmed to sweep forward and backward (using an SMU, as said) while the drain current is measured (again, using SMUs).

These curves allow us to collect useful data to precisely model the activation and deactivation of the transistor conductivity, analyze when the characteristic reflects linearity or enters a saturation behavior, and determine how much a self-heating effect can potentially shift these parameters and curves.

When the characterization refers to modeling the behavior of charge carriers, electrons, or holes that jump between states and modify their mobility according to several conditions, the measurement system connects to the DUT in a four-wire (or remote sense) configuration and uses triax cables.

Looking at the triax cable connection in a four-wire configuration, the total length corresponds to the sum of the Force Hi and the Sense Hi cable lengths.

Based on the capacitance/meter (pF/m) specification of the triax cable, we can calculate the capacitance of two triax cables connecting the SMUs to the device terminals with a length of 20 meters (10m + 10m) to be around 2 nF for the guard capacitance and 6 nF for the shield capacitance.

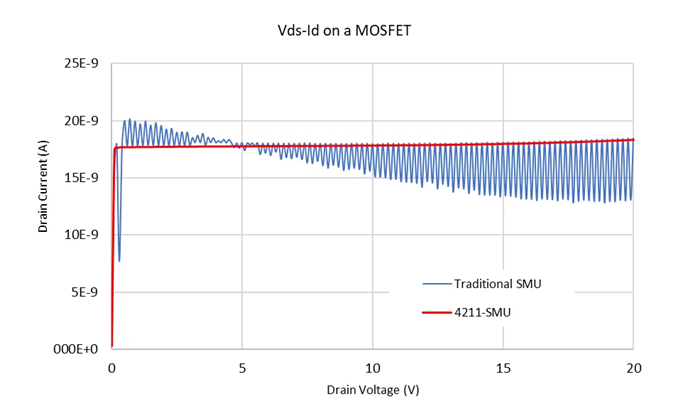

The sensitivity of the SMUs in these cases will be pointless when measuring the transfer characteristic at low current (nanoamps typically) levels, since the capacitance cable loading will cause oscillations.

The SMUs’ sensitivity must be combined with the ability to sustain significant capacitances caused by the cabling load, or the load of any lead that connects the SMUs to the DUT.

If this is not the case, the sensitivity will be useless, and the SMU will produce only noisy oscillating readings.

Id-Vd curves of a FET measured through a switch matrix using two traditional SMUs vs. two 4211-SMUs

The ability to identify whether test capacitance is affecting your measurement is becoming more and more critical. Keithley application engineers are indeed providing valuable consulting in these situations to make sure customers avoid these pitfalls.

Whenever long connecting cables are present in the setup, or switch matrices are between the measurements system and the DUT, or in all cases where the DUT on chuck requires you to enter the range of nanoamps measurements, it’s critical to review the setup and ask for some consulting.

New solutions for the critical ranges

Under these special challenging conditions, it might be necessary to use specific SMUs modules for the measurements.

Keithley has released a special version of the SMUs that work in parameter analysis systems like the 4200A-SCS parameter analyzer.

SMUs are ideal for connecting to LCD test stations, probers, switch matrices or any other large or complicated tester

The 4201-SMU Medium Power SMU and 4211-SMU High Power SMU (with the optional 4200-PA Preamp) grant stable low current measurements, even in applications with high test connection capacitance load due to long cabling connections.

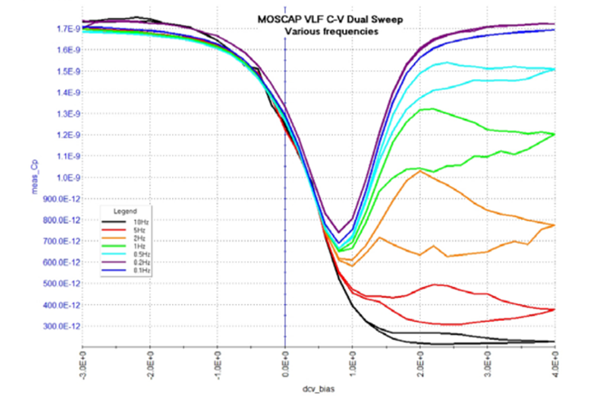

C-V Measurement for High Impedance Applications

In fact, these modules can source into and measure a system that is 1,000 times more capacitive than what's possible today. For example, if the current level is between 1 to 100 pA (picoamp), the new Keithley modules can be stable with as much as 1 µF (microfarad) of load capacitance. In contrast, the maximum load capacitance competitive units can tolerate before measurement stability degrades is just 1,000 pF (picofarad), or 1,000 times worse.

Conclusions

Ongoing improvements of measurement technologies are necessary in the effort to optimize semiconductor materials for integrated transistors with low contact resistance, special geometries, and unique structures.

The success of GaN transistors for future power electronics is closely connected to the nanostructures used in their fabrication process. On one hand, lower capacitances in the gate width structure raise the problem of considering any other significative capacitance contributions, like the one coming from cabling and connectivity. On the other hand, they overcome problems by improving the SMU’s ability to withstand high capacitances providing higher measurement stability.