By Dave Akerson

Editor’s note: This is the third part in a 3-part series focused on PCI Express and the next generation PCIe 5.0 specification. In this installment, we look at PCIe 5.0 receiver testing and debugging considerations.

In Part 2 of this series, we looked at the PCIe specification changes likely to be required to support the transition from PCIe Gen4 rates (16 GT/s) to Gen5 rates (32 GT/s). As you can imagine, significantly smaller eye openings will make testing these designs much more challenging. In this post, we’ll look at receiver calibration, test, and debugging tools and techniques to help address those challenges and get your designs validated and into production faster. It’s time to turn sci-fi into reality.

Calibration

Those of you familiar with receiver testing know that before testing can proceed, the impairments, or stresses, that will be presented to the receiver must be calibrated as close to the device under test (DUT) receiver as possible. Before adding any stress, it’s important to employ a signal generator that provides clean and consistent output as any signal irregularities will most likely create problems in achieving the stress targets. You also will not want to over or under stress your device, so careful calibration leads to more accurate and repeatable results.

The target stress impairments are defined in the PCIe specifications and include the addition of channel loss or ISI, random jitter, sinusoidal jitter, and interference to the compliance data pattern. Calibration is performed by capturing the signal waveforms using a real-time oscilloscope, and then analyzing the waveform using an analysis tool called SIGTEST, which projects the eye opening at the receiver after the package and equalization models are applied.

So far, so good. The challenge, however, is in getting consistent measurement results. The key here is good calibration automation.. For PCIe Gen5, up to 20 measurements may be required for each test condition, which can mean that literally hundreds of tests points need to be evaluated. It would be extremely tedious and time consuming to attempt this manually. Tektronix solutions not only automate this process, but accelerate the data analysis by allowing up to 20 waveforms to be evaluated simultaneously. Go have lunch -- and your calibration can be complete when you return!

Link Equalization

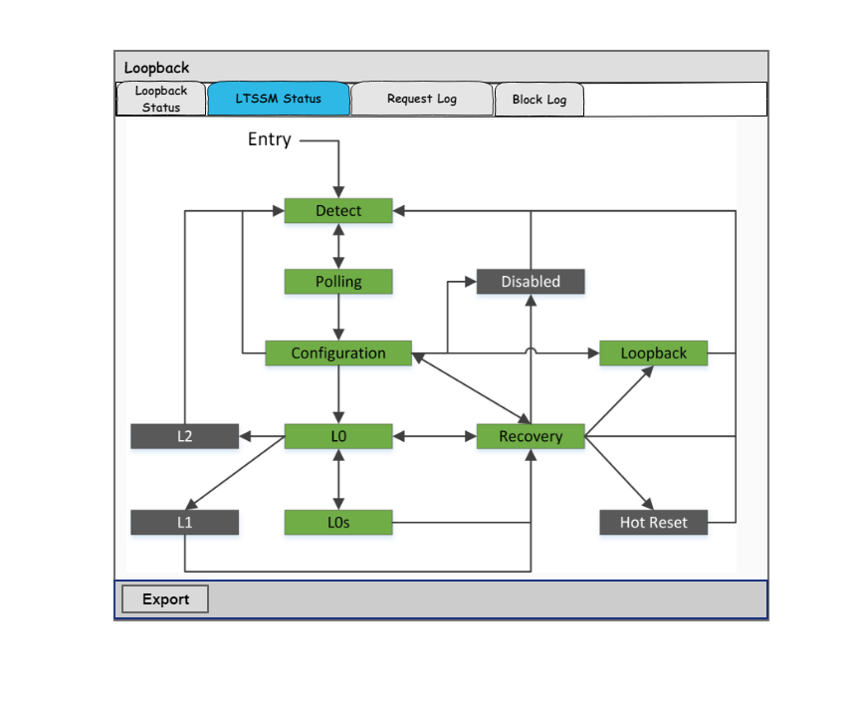

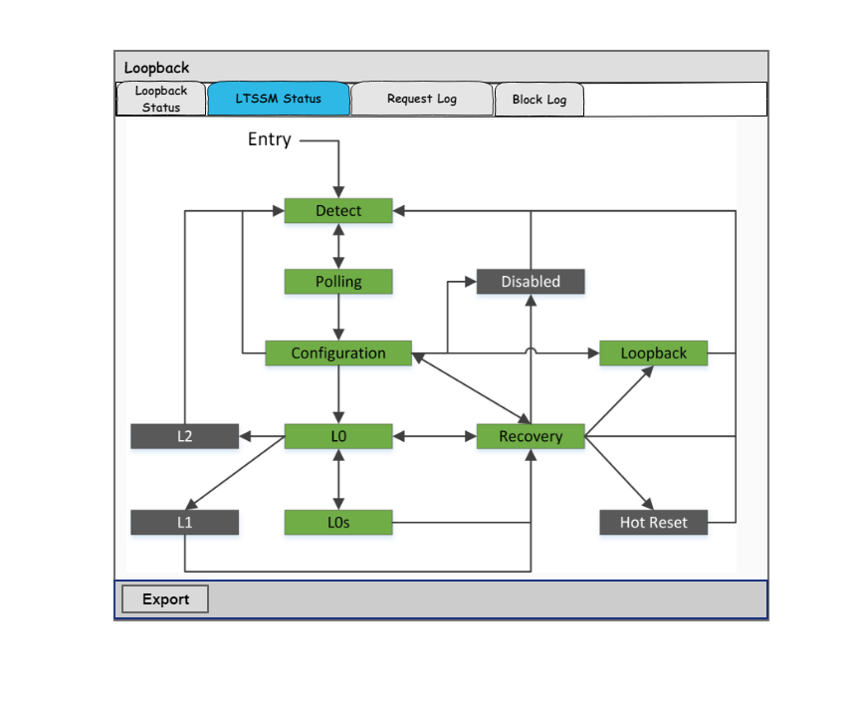

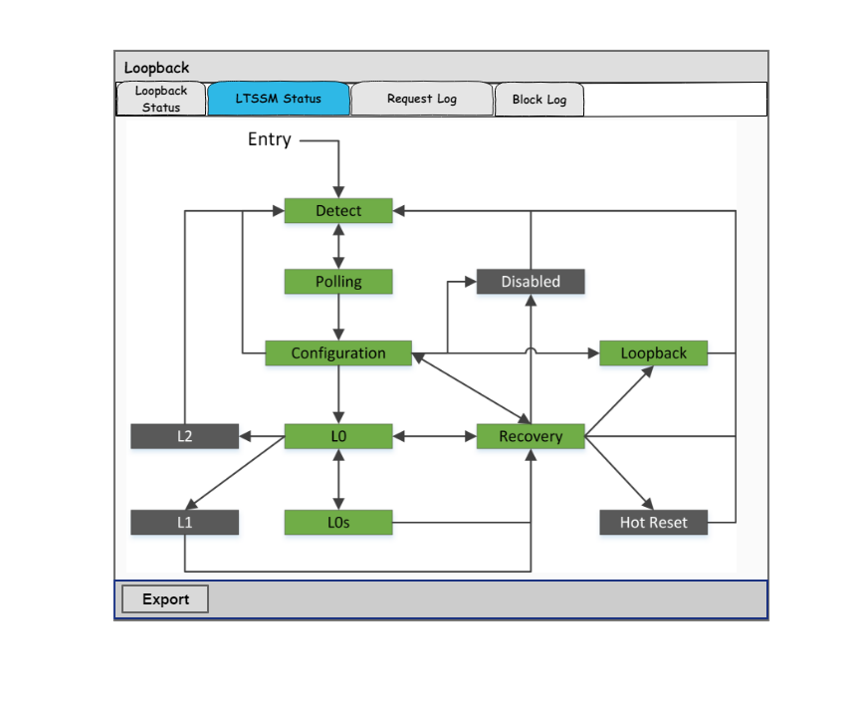

Okay, the calibration is done and you’re ready to test, right? Well, not so fast. Before testing can proceed, the DUT must be placed into test mode, or loopback. What’s more, with PCIe Gen5, the DUT will also need to complete link equalization training -- i.e. through “recovery” phase -- before the receiver test can proceed. All of this is implemented via the PCIe link training and status state machine (LTSSM), and for testing involves protocol-based handshaking between the DUT and the bit error rate tester.

Unfortunately, in many of the cases we’ve encountered, handshaking can be problematic, typically when different interpretations of the LTSSM or timing issues prevent completion of the process. It’s also important to meet the strict 500 ns response time requirements of the specification. This is where having full protocol handshaking and built-in protocol-based debugging tools can be essential to keeping the DUT evaluation moving forward.

The BSX-series BERTScope® provides unprecedented visibility into the progress of the LTTSM and a variety of tools for identifying where and when problems occur. The ability to capture received traffic, and decode into PCIe protocol messages, combined with the ability to cross trigger and decode messages with Tektronix real-time oscilloscopes can help identify and move past blocking issues. Having quickly resolved any handshaking issues, you are ready to move on to link equalization and compliance or characterization testing.

Testing the DUT

Congratulations, you are now ready to proceed to testing your DUT. Success in receiver testing PCIe devices is achieved by proving that with the calibrated stresses presented to the receiver, the measured BER (bit error rate) of the looped-back data is one or fewer errors in 1012 bits evaluated. At 32 GT/s for PCIe Gen5, this test is fast; typically, just over 30 seconds of test time.

If you meet the BER requirement, you can move on to the next test point. But what if the DUT is producing errors? How do you track down the root cause, particularly at a data rate of 32 GT/s? Fortunately, the BERTScope has a unique error analysis tool available to help track down the source of the errors. By logging actual bit error locations, this tool allows you to visualize error patterns that can often be tracked to a specific problematic functional element in the DUT.

For example, the ability to correlate errors directly to bit location in the test pattern using the pattern sensitivity tool might lead you to identify issues with a PLL or threshold detector within the DUTs receiver. We like to think of this capability as “virtual probing” of the DUT, and you might be interested in a recent white paper describing this tool in more detail.

When a scope is required, Tektronix offers the Serial Data Link Analysis (SDLA) tool for performing equalization, embedding, clock recovery and simulation. Add to that our DPOJET PCIe electrical signal evaluation and validation tool and you have a complete tool kit and solution available from a single vendor.

Choice of test tools critical

The increase in the PCIe Gen5 channel rate to 32 GT/s is tightening calibration and test requirements across the board, making the choice of test tools more critical than ever. With the calibration and test automation tools available, combined with the unique debugging tools available with the Tektronix DPO70000SX series real-time oscilloscope and BERTScope BSX-series bit error rate tester, you will be well positioned to complete characterization and compliance testing with a single approved instrument for all of the PCIe generations, including Gen5.

As mentioned in earlier blog posts, the Tektronix PCIe solution does not require you to purchase new hardware for PCIe 5.0 testing. Our current PCIe solutions support Gen5 Phy evaluations today and previous generations of PCIe including PCIe Gen3 and PCIe Gen4. Our current solution is also upgradeable to support PCIe 5.0 handshaking. This allows you to future proof your test and measurement investments to meet your current and future PCIe needs

For more information, visit https://www.tek.com/wired-communications/accelerate-pcie-sas-sata-test-and-debug.

For Part 1 of this series, visit https://www.tek.com/blog/pci-express-it-science-fiction-or-just-great-engineering.

For Part 2, visit https://www.tek.com/blog/pcie-making-science-fiction-capabilities-reality.