DesignCon 2023 is happening January 31 – February 2, 2023 at the Santa Clara Convention Center in Santa Clara, CA and we’ll be at Booth 727. Swing by and we’ll show you – in real time – practical applications to solve current and emerging test challenges.

Here’s what you’ll find…

Deep Dive Into DDR5 and LPDDR5/5X

Explore the Tektronix memory solutions (leveraging powerful analysis tools) on AMD’s advanced server platform. By using Tektronix’ P7700 series high impedance probes, along with Nexus XH series interposers, design and validation engineers can capture DDR waveforms with high signal fidelity. From there, the TekExpress DDR compliance software can be easily used to quickly automate, measure, and validate DDR5 and LPDDR5X designs.

Unique Probing Connections for Power and Signal Integrity

With more demanding, higher speed components per board, analyzing Power Rail and Power Distribution Networks for channel-to-channel interference is a critical piece in design validation. This is especially true while under load in various operating conditions. Using the unique capabilities of the 6 Series B Oscilloscope with application specific probes, design and validation engineers can accurately correlate voltage, current, and EMI signals to quickly identify sources of error and propose corrections.

A Demonstration of a Complete System Solution for 802.3ck, 10-112 Gb/s Per Lane Ethernet and PCIe® Gen1-Gen6

The Tektronix DPO70000SX Real Time Oscilloscope is a complete electrical solution for full compliance testing or system debugging – for the latest 802.3ck, for previous 50G/per lane standards, and PCIe.

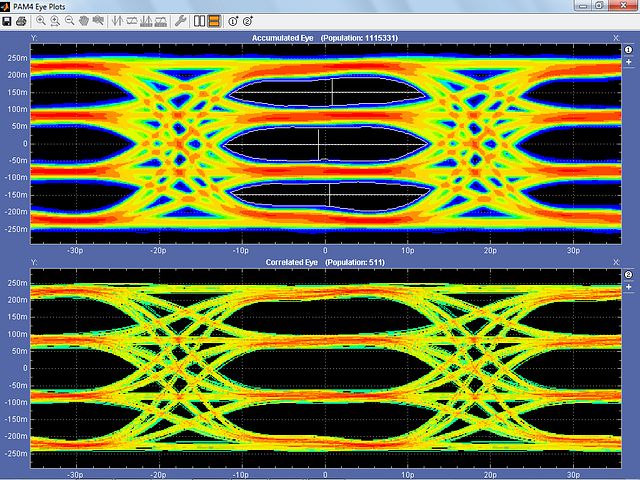

A new approach for modeling complex PAM4 SerDes receiver equalizers using Conditional Generative Adversarial Networks (cGAN)

cGAN modeling takes place with no knowledge of the receiver equalizer structures. The engine can be configured to generate Bit-Error Rate (BER) contour, voltage contour as well as eye-diagram outputs that are indistinguishable from ground truth measurements produced by the Tektronix PAMJET Signal Analysis software.

There will also be two NEW demos, including…

Margin Tester for Fast PCIe Link Health Evaluation

We’ll demo the industry-first PCIe Link Health Evaluation solution from Tektronix: the TMT4 Margin Tester. This new product category enables design, validation, and failure analysis teams to assess the link health of the PCIe Gen 3 and Gen 4 devices in just minutes – not hours or days like legacy test solutions.

Automated PCIe 6.0 Base Tx/Rx Testing at 64 GT/s

Industry-first automated testing solution for PCI Express® 6.0 Base transmitter and receiver testing at 64 GT/s. Wizard-based user interface simplifies calibration and measurement complexities of PAM-4 signaling. Supports backward compatibility of full compliance testing for mainstream generation - PCIe 5.0 / 4.0, Base and CEM.

Tektronix will participate in the following sessions:

Measuring PSNR/PSRR/PSMR to Meet QSFP/OSFP High-Speed Requirements

In this tutorial, we focus on PSRR, PSMR, and PSNR which are all measures of how power rail noise appears at the output of voltage regulators, RF amplifiers, and digital channel jitter. PSNR on 400/800G transceivers will be a focus. The test solution using the P2124A, the first water cooled testing probe for PSNR noise immunity applications is explored. Live demonstrations of PSRR testing of power supplies using a 6 Series B Oscilloscope, PSMR using Signal View software, and PSNR using a 112Gb/s PAM-4 – PCIe application will be presented. (1/31, 9am in Ballroom E)

The Case of the Closing Eyes: Bridging FEC to Signal Integrity

Forward Error Correction (FEC) is a key enabler for high-speed communications designs. This panel of experts will discuss the role FEC plays and how it can be impacted by signal integrity challenges; and what to do with a testing architecture designed to help find a bridge between FEC and Signal Integrity. Join this session for a lively debate on the topic. (1/31. 4:45pm in Ballroom GH)

PCIe 6.0: Challenges of Achieving 64GT/s with PAM4 in Lossy, HVM Channels

This panel will focus on the latest evolution of PCI Express Technology, revision 6.0 of the PCIe spec, which uses PAM4 rather than NRZ signaling of previous PCIe revisions. PCI Express technology’s advances to 64GT/s has enabled system designers to achieve much needed and desired improvements in data throughput aiding advances in the deployment of artificial intelligence inference engines and co-processors in the data center. (1/31, 4:45pm in Ballroom F)

Towards 106 GBaud: Analysis of Latest 53 GBaud DUTs Informs the Improvements of Methodology

With the understanding of the behavior of the devices with the settings of the current standard, we’ll run experiments with the different proposed changes, such as measurement bandwidth filters current and proposed for 106 GBaud, and proposed equalizations – all scaled to the symbol rate of our existing commercial devices. We will analyze in detail the part that only a few optical standards explicitly mention although it impacts both electrical and optical signals’ measurements alike: the end of measurement filter compliance. (2/1, 8am in Ballroom F)

Data-Driven PAM4 SerDes Modeling & Generative Adversarial Network

This paper will describe a novel method to model complex PAM4 SerDes using cGAN. Modeling is based on deep learning using data from test instrument captures or chip internal measurements. No knowledge of the SerDes equalizer structures such as CTLE or DFE is required to generate the model. (2/2, 11:15am in Ballroom G)

To learn more about DesignCon 2023 and Tektronix’s presence at the show, download our show flyer. We hope to see you in Santa Clara!