Свяжитесь с нами

Живой чат с представителями Tektronix. С 9:00 до 17:00 CET

Звонок

Позвоните нам

С 9:00 до 17:00 CET

Загрузить

Загрузить руководства, технические описания, программное обеспечение и т. д.:

Обратная связь

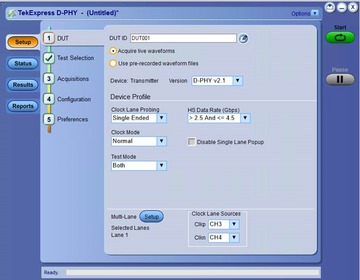

TekExpress MIPI D-PHY Test Application

Datasheet

Дополнительные сведения

- ПО анализа для осциллографов

- Поддержка приборов

- DPO70000SX

- MSO/DPO70000

- MSO серии 6 B

- $name

- Explore more Software models